Odomknutie sily vysokorýchlostnej pamäte: Ako dizajn HBM rozhrania revolucionalizuje akcelerátory AI v roku 2025 a ďalej. Preskúmajte technológie, rast trhu a strategické príležitosti formujúce ďalšiu éru hardvéru AI.

- Hlavné zhrnutie: Kľúčové nálezy a strategické poznatky

- Prehľad trhu: Dizajn HBM rozhrania pre akcelerátory AI v roku 2025

- Technologická krajina: Evolúcia štandardov a architektúr HBM

- Konkurenčná analýza: Vedúci hráči a trendy v inováciách

- Veľkosť trhu a predpoveď (2025–2030): CAGR, projekcie príjmov a regionálne rozdelenie

- Hlavné faktory a výzvy: Požiadavky na výkon, energetická efektívnosť a zložitosti integrácie

- Emergentné aplikácie: AI, HPC, dátové centrá a okrajové výpočty

- Analýza dodávateľského reťazca a ekosystému

- Budúci výhľad: Disruptívne technológie a HBM rozhrania novej generácie

- Strategické odporúčania pre zainteresované strany

- Zdroje a odkazy

Hlavné zhrnutie: Kľúčové nálezy a strategické poznatky

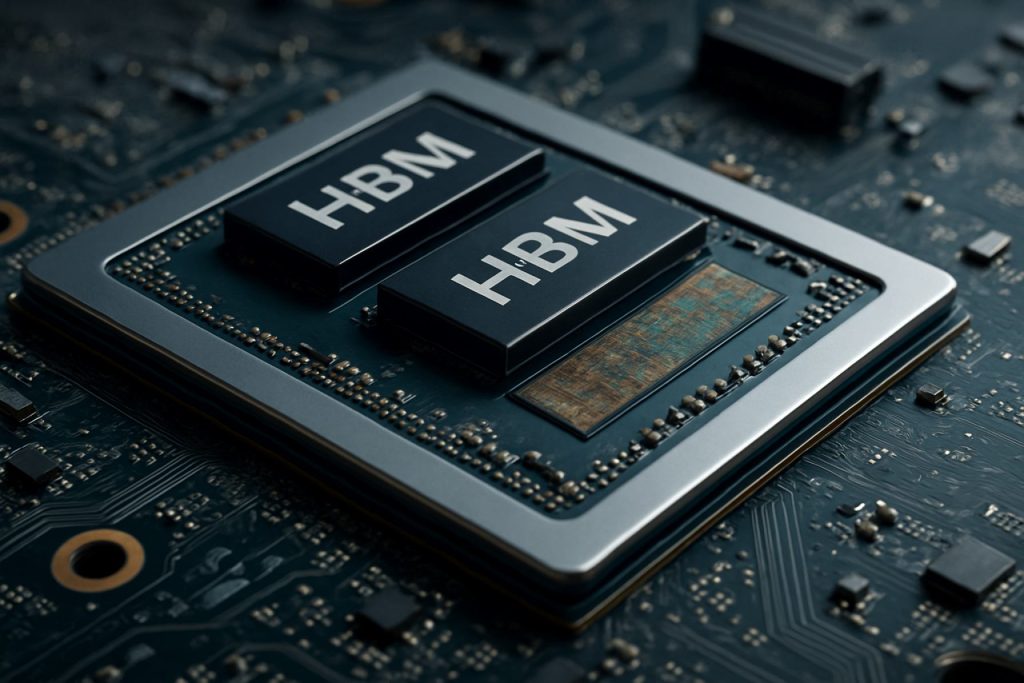

Dizajn rozhrania s vysokorýchlostnou pamäťou (HBM) sa ukázal ako kritický faktor pre akcelerátory AI budúcej generácie, zameriavajúci sa na rastúce požiadavky na pamäťovú šírku pásma, energetickú efektívnosť a kompaktné formáty v aplikáciách náročných na dáta. V roku 2025 sa rýchla evolúcia pracovných záťaží AI—najmä v hlbokom učení a veľkých jazykových modeloch—znásobila potrebu pamäťových riešení, ktoré môžu poskytovať terabajty za sekundu šírky pásma pri minimalizácii latencie a spotreby energie. HBM, so svojou 3D-stohovanou architektúrou a technológiou cez kremík (TSV), sa stal preferovaným pamäťovým rozhraním pre popredných predajcov akcelerátorov AI.

Kľúčové zistenia ukazujú, že adopcia HBM3 a očakávané uvedenie HBM4 nastavujú nové štandardy v šírke pásma, pričom HBM3 ponúka až 819 GB/s na zásobník a HBM4 by mal presiahnuť 1 TB/s. Tieto pokroky umožňujú akcelerátorom AI spracovávať väčšie súbory údajov v reálnom čase, výrazne zlepšujúce výkonnosť tréningu a odvodzovania. Hlavní hráči v odvetví, ako sú Samsung Electronics Co., Ltd., Micron Technology, Inc. a SK hynix Inc., sú na čele inovácií HBM a úzko spolupracujú s dizajnérmi hardvéru AI na optimalizácii protokolov rozhrania a integrity signálu.

Strategické poznatky naznačujú, že úspešný dizajn rozhrania HBM závisí od niekoľkých faktorov: pokročilé techniky balenia (ako sú 2.5D a 3D integrácie), robustné tepelné riadenie a spoludizajn pamäťových ovládačov s jadrami spracovania AI. Spoločnosti ako Advanced Micro Devices, Inc. a NVIDIA Corporation využívajú tieto stratégie na dodanie akcelerátorov AI s bezprecedentnými výkonnostnými metrikami na watt. Okrem toho integrácia HBM s architektúrami založenými na čipletách získava na popularite, ponúkajúc modularitu a škálovateľnosť pre budúce systémy AI.

V budúcnosti sa očakáva, že ekosystém HBM rozhraní bude ťažiť zo snáh o standardizáciu, ktoré vedú organizácie ako JEDEC Solid State Technology Association, ktoré zjednodušujú interoperabilitu a urýchľujú uvedenie nových pamäťových riešení na trh. Ako sa AI modely naďalej stávajú zložitými, strategické zosúladenie dizajnu rozhrania HBM s vyvíjajúcimi sa pracovnými záťažami AI bude kľúčové pre udržanie konkurencieschopnosti v oblasti hardvéru AI.

Prehľad trhu: Dizajn HBM rozhrania pre akcelerátory AI v roku 2025

Trh s dizajnom rozhrania s vysokorýchlostnou pamäťou (HBM) v akcelerátoroch AI je pripravený na významný rast v roku 2025, poháňaný rastúcimi výpočtovými požiadavkami pracovných záťaží v oblasti umelej inteligencie a strojového učenia. HBM, technológia 3D-stohovanej DRAM, ponúka významné zlepšenia v šírke pásma pamäte a energetickej efektívnosti v porovnaní s tradičnými pamäťovými riešeniami, čím sa stáva kritickým faktorom pre akcelerátory AI budúcej generácie.

V roku 2025 sa adopcia HBM rozhraní urýchľuje poprednými polovodičovými spoločnosťami a prevádzkovateľmi hyperskalových dátových centier, ktorí sa snažia prekonať pamäťové úzke hrdlá vlastné úlohám v tréningu a odvodzovaní AI. Najnovšie štandardy HBM, ako HBM3 a vznikajúci HBM3E, poskytujú šírky pásma presahujúce 1 TB/s na zariadenie, ktoré podporujú paralelné spracovanie požiadaviek veľkých jazykových modelov a generatívnych AI systémov. Spoločnosti ako Samsung Electronics Co., Ltd., Micron Technology, Inc. a SK hynix Inc. sú na čele vývoja HBM a dodávajú pamäťové riešenia, ktoré sú rýchlo integrované do dizajnov akcelerátorov AI.

Dizajn rozhrania pre HBM v akcelerátoroch AI je čoraz zložitejší, vyžadujúci pokročilé technológie balenia, ako sú 2.5D a 3D integrácie. Tieto prístupy umožňujú blízku fyzickú blízkosť zásobníkov HBM k spracovateľským jednotkám, minimalizujúc latenciu a maximalizujúc prenos dát. Polovodičové továrne ako Taiwan Semiconductor Manufacturing Company Limited (TSMC) a Intel Corporation investujú do pokročilých interposer a balících riešení na podporu týchto architektúr.

Dopyt po akcelerátoroch AI s HBM je obzvlášť silný v oblastiach cloudových dátových centier, okrajového výpočtu a vysokovýkonného počítačovania (HPC). Hlavní dodávatelia AI čipov, vrátane NVIDIA Corporation a Advanced Micro Devices, Inc. (AMD), integrujú HBM do svojich vlajkových produktov na poskytnutie potrebnej pamäťovej šírky pásma pre najmodernejšie AI modely. Konkurencieschopnosť trhu je ďalej formovaná vyvíjajúcimi sa štandardmi od organizácií ako JEDEC Solid State Technology Association, ktoré naďalej definujú nové HBM špecifikácie na splnenie budúcich požiadaviek AI.

Celkovo je trh s dizajnom HBM rozhraní pre akcelerátory AI v roku 2025 charakterizovaný rýchlou inováciou, strategickými partnerstvami v polovodičovom dodávateľskom reťazci a neúnavným zameraním na šírku pásma, energetickú efektívnosť a škálovateľnosť na podporu ďalšej vlny pokroku v oblasti AI.

Technologická krajina: Evolúcia štandardov a architektúr HBM

Technologická krajina pre dizajn rozhrania s vysokorýchlostnou pamäťou (HBM) sa rýchlo vyvíjala, aby vyhovela rastúcim požiadavkám akcelerátorov AI. Od jeho zavedenia HBM prešiel niekoľkými generáciami zlepšení, pričom každá iterácia priniesla vyššiu šírku pásma, zvýšenú kapacitu a vylepšenú energetickú efektívnosť. Počiatočný štandard HBM, vyvinutý spoločnosťami Samsung Electronics Co., Ltd. a SK hynix Inc. v spolupráci s Advanced Micro Devices, Inc. (AMD), pripravil pôdu pre vertikálne stohovanie DRAM čipov a ich prepojenie cez kremíkové viazania (TSV), umožňujúce širokú I/O a nízku spotrebu energie.

Štandardy HBM2 a HBM2E, ratifikované organizáciou JEDEC Solid State Technology Association, ďalej zvýšili šírku pásma a kapacitu na zásobník až do 3,6 Gbps na pin a 16 GB na zásobník. Tieto zlepšenia boli kritické pre akcelerátory AI, ktoré vyžadujú rýchly prístup k veľkým súborom údajov a modelom. Najnovší štandard HBM3, zavedený v roku 2022, posúva šírku pásma na viac ako 6,4 Gbps na pin a kapacity zásobníka až do 24 GB, pričom Micron Technology, Inc. a SK hynix Inc. patrí medzi prvé, ktoré ohlásili produkty HBM3. Očakáva sa, že HBM3E, ktorý by mal byť široko prijatý v roku 2025, prinesie ešte vyššie rýchlosti a vylepšené tepelné riadenie, čím sa splnia potreby pracovných záťaží AI budúcej generácie.

Architektonicky sa integrácia HBM s akcelerátormi AI posunula z tradičného umiestnenia PCB vedľa seba na 2.5D a 3D balenie, ako sú kremíkové interposery a pokročilý dizajn čipletov. NVIDIA Corporation a AMD boli priekopníkmi vo využívaní HBM vo svojich GPU a akcelerátoroch AI, využívajúc tieto technológie balenia na minimalizovanie straty signálu a maximalizáciu pamäťovej šírky pásma. Adopcia spoločne balených optík a pamäťových ovládačov na čipe sa nakoniec stáva bežnou praxou, pričom ďalšie znižujú latenciu a spotrebu energie.

Pohľad na rok 2025 naznačuje, že krajina dizajnu rozhrania HBM bude zameraná na škálovateľnosť, energetickú efektívnosť a flexibilitu integrácie. Hlavní hráči odvetvia spolupracujú na nových štandardoch a referenčných architektúrach, aby zabezpečili interoperabilitu a podporili exponenciálny rast veľkosti a zložitosti AI modelov. Ako akcelerátory AI naďalej posúvajú hranice výkonu, evolúcia štandardov a architektúr HBM zostane základným kameňom inovácií v tejto oblasti.

Konkurenčná analýza: Vedúci hráči a trendy v inováciách

Konkurenčné prostredie pre dizajn rozhrania s vysokorýchlostnou pamäťou (HBM) v akcelerátoroch AI sa rýchlo mení, poháňané rastúcimi požiadavkami pracovných záťaží v oblasti umelej inteligencie a potrebou efektívneho a rýchleho prenosu údajov medzi pamäťovými a spracovateľskými jednotkami. Kľúčoví hráči v odvetví ako Samsung Electronics Co., Ltd., Micron Technology, Inc. a SK hynix Inc. dominujú v sektore výroby HBM a každý zavádza po sebe idúce generácie HBM (HBM2E, HBM3 a ďalej) s vyššou šírkou pásma, kapacitou a energetickou efektívnosťou.

Na fronte akcelerátorov AI spoločnosti ako NVIDIA Corporation a Advanced Micro Devices, Inc. (AMD) integrovali HBM do svojich vlajkových GPU a akcelerátorov dátových centier, využívajúc široké rozhranie pamäte a 3D stohovanie na minimalizovanie úzkych hrdiel v aplikáciách hlbokého učenia a vysokovýkonného počítačovania. Intel Corporation taktiež prijal HBM vo svojich produktoch AI a HPC, zameriavajúc sa na optimalizáciu rozhrania pre nižšiu latenciu a vyšší prenos údajov.

Inovačné trendy v dizajne HBM rozhrania sú zamerané na maximalizáciu šírky pásma pri súčasnom znižovaní spotreby energie a fyzického priestoru. Techniky ako pokročilé architektúry cez kremíkové viazanie (TSV), zlepšená integrita signálu a dynamické napätie/frekvenčné škálovanie sa implementujú na riešenie týchto výziev. Adopcia štandardu HBM3 a vývoj HBM4, vedené JEDEC Solid State Technology Association, posúvajú hranice pamäťovej šírky pásma, pričom HBM3 cieli na rýchlosti presahujúce 800 GB/s na zásobník a HBM4 sa očakáva, že túto hranicu signifikantne presiahne.

Ďalším významným trendom je spolubalenie HBM s akcelerátormi AI pomocou pokročilých baliacich technológii ako 2.5D a 3D integrácia. Taiwan Semiconductor Manufacturing Company Limited (TSMC) a Amkor Technology, Inc. sú na čele poskytovania týchto baliacich riešení, čo umožňuje bližšiu integráciu a lepšie tepelné riadenie. Tento prístup spoludizajnu je kritický pre systémy AI budúcej generácie, kde pamäťová šírka pásma a blízkosť k výpočtovým jednotkám priamo ovplyvňujú výkon a efektívnosť.

Na záver, konkurenčná dynamika v dizajne HBM rozhraní pre akcelerátory AI je formovaná rýchlou inováciou, strategickými partnerstvami medzi výrobcami pamäte a čipmi a neúnavným úsilím o vyššiu šírku pásma a nižší energetický výkon s cieľom uspokojiť potreby pracovných záťaží poháňaných AI.

Veľkosť trhu a predpoveď (2025–2030): CAGR, projekcie príjmov a regionálne rozdelenie

Trh s dizajnom rozhrania s vysokorýchlostnou pamäťou (HBM) pre akcelerátory AI je pripravený na robustný rast v období medzi 2025 a 2030, poháňaný rastúcim dopytom po vysokovýkonnom počítačovaní v oblastiach umelej inteligencie, strojového učenia a aplikácií v dátových centrách. Celosvetový trh HBM rozhraní sa očakáva, že zaregistruje zloženú ročnú mieru rastu (CAGR) približne 25 až 30 % počas tohto obdobia, čo odráža rýchlu adopciu akcelerátorov AI umožnených HBM v podnikových a cloudových prostrediach.

Projekcie príjmov naznačujú, že veľkosť trhu, ocenená na odhadovaných 2,5 miliardy dolárov v roku 2025, by mohla presiahnuť 7,5 miliardy dolárov do roku 2030. Tento nárast je pripisovaný rastúcej integrácii HBM do akcelerátorov AI novej generácie, ktoré vyžadujú ultra-rýchle pamäťové rozhrania na zvládanie masívnych paralelných pracovných záťaží. Kľúčoví hráči v odvetví ako Samsung Electronics Co., Ltd., Micron Technology, Inc. a SK hynix Inc. intenzívne investujú do výskumu a vývoja na pokrok technológií HBM rozhraní, čím ďalej poháňajú rozšírenie trhu.

Regionálne, ázijsko-pacifická oblasť sa očakáva, že bude dominovať na trhu dizajnu HBM rozhraní, pričom získa viac ako 45 % celosvetových príjmov do roku 2030. Táto dominancia je podložená prítomnosťou hlavných polovodičových tovární a výrobcov pamäte v krajinách ako Južná Kórea, Taiwan a Čína. Severná Amerika nasleduje blízko, poháňaná koncentráciou vývojárov akcelerátorov AI a hyperskalových dátových centier v Spojených štátoch a Kanade. Európa tiež zaznamenáva stabilný rast, najmä v sektoroch automobilovej AI a priemyselnej automatizácie.

Rozšírenie aplikácií poháňaných AI v okrajových výpočtoch, autonómnych vozidlách a vysokofrekvenčnom obchodovaní ďalej urýchľuje adopciu pokročilých HBM rozhraní. Ako sa modely AI stávajú zložitejšími a náročnejšími na údaje, potreba vyššej pamäťovej šírky pásma a nižšej latencie tlačí dizajnérov čipov k prijatiu štandardov HBM2E, HBM3 a vznikajúceho HBM4, ako je definované JEDEC Solid State Technology Association.

Na záver, trh dizajnu HBM rozhraní pre akcelerátory AI je nastavený na výrazné rozšírenie do roku 2030, s silným regionálnym rastom v ázijsko-pacifickej oblasti a Severnej Amerike, a jasným trendom smerom k vyššej šírke pásma a energeticky efektívnejším pamäťovým riešeniam.

Hlavné faktory a výzvy: Požiadavky na výkon, energetická efektívnosť a zložitosti integrácie

Rýchla evolúcia pracovných záťaží umelej inteligencie (AI) kladie bezprecedentné požiadavky na pamäťové subsystémy, čím sa vysokorýchlostná pamäť (HBM) stáva kritickým faktorom pre akcelerátory AI budúcej generácie. Dizajn HBM rozhraní musí adresovať niekoľko kľúčových faktorov a výziev, najmä v oblasti výkonu, energetickej efektívnosti a zložitosti integrácie.

Požiadavky na výkon: Akcelerátory AI vyžadujú masívnu pamäťovú šírku pásma na zásobovanie dátovo náročných výpočtových jadier, najmä pri modeloch hlbokého učenia s miliardami parametrov. HBM, so svojou 3D-stohovanou architektúrou a širokou I/O, ponúka šírky pásma presahujúce 1 TB/s v najnovších generáciách. Avšak dosiahnutie tohto v praxi si vyžaduje starostlivý dizajn rozhrania na minimalizáciu latencie, maximalizáciu prenosu dát a zabezpečenie integrity signálu pri vysokých dátových rýchlostiach. Rozhranie musí tiež podporovať efektívne vzory pohybu údajov typické pre pracovné záťaže AI, ako sú veľké matice násobení a operácie s tenzormi, ktoré kladú dodatočné nároky na pamäťové ovládače a prepojenia.

Energetická efektívnosť: Ako akcelerátory AI narastajú, spotreba energie sa stáva kritickým obmedzením, ako pre nasadenia v dátových centrách, tak aj pre okrajové aplikácie. Blízkosť HBM k procesoru a jeho použitie cez kremíkové viazania (TSV) znižujú energiu na bit v porovnaní s tradičnou DDR pamäťou. Napriek tomu musí dizajn rozhrania ďalej optimalizovať energiu použitím pokročilých signálnych techník, dynamického napätia a frekvenčného škálovania a inteligentného správy energie. Vyváženie vysokej šírky pásma s nízkym energetickým výkonom je pretrvávajúcou výzvou, najmä keď pamäťové zásobníky narastajú na kapacite a rýchlosti. Organizácie ako Samsung Electronics Co., Ltd. a Micron Technology, Inc. aktívne vyvíjajú nové generácie HBM s vylepšenou energetickou efektívnosťou.

Zložitosti integrácie: Integrácia HBM s akcelerátormi AI zahŕňa významné výzvy balenia a systémovej úrovne. Fyzické stohovanie pamäťových čipov a ich prepojenie s procesorom cez kremíkové interposery alebo pokročilé substráty vyžaduje presnú výrobu a tepelné riadenie. Integrita signálu, elektromagnetické rušenie a mechanický stres musia byť všetky pokryté na zabezpečenie spoľahlivého fungovania. Okrem toho musí byť rozhranie kompatibilné s vyvíjajúcimi sa štandardmi, ako sú tie, ktoré definovala JEDEC Solid State Technology Association, aby sa zabezpečila interoperabilita a budúca škálovateľnosť. Zložitosti sa zvyšujú, keď akcelerátory prijímajú architektúry založené na čipletách, čo si vyžaduje robustné HBM riešenia rozhrania, ktoré dokážu podporovať heterogénnu integráciu.

Na záver, dizajn HBM rozhraní pre akcelerátory AI v roku 2025 je formovaný potrebou poskytovať extrémnu šírku pásma, udržiavať energetickú efektívnosť a zvládať zložitosti pokročilej integrácie, pričom nezabudla na rýchlu inováciu v oblasti hardvéru AI.

Emergentné aplikácie: AI, HPC, dátové centrá a okrajové výpočty

Rýchla evolúcia umelej inteligencie (AI), vysokovýkonného počítačovania (HPC), dátových centier a okrajových výpočtov poháňa bezprecedentný dopyt po pamäťovej šírke pásma a efektívnosti. Dizajn rozhrania s vysokorýchlostnou pamäťou (HBM) sa stal základnou technológiou pre akcelerátory AI, umožňujúc masívnu paralelizáciu a prenos údajov potrebný pre moderné pracovné záťaže hlbokého učenia a analytiky. HBM to dosahuje stackingom viacerých DRAM čipov vertikálne a ich prepojením cez kremíkové viazania (TSV), čo vedie k významne vyššej šírke pásma a nižšej spotrebe energie v porovnaní s tradičnými pamäťovými rozhraniami.

V akcelerátoroch AI, ako sú tie vyvinuté NVIDIA Corporation a Advanced Micro Devices, Inc. (AMD), sú HBM rozhrania kritické na zásobovanie údajov tisíckam spracovateľských jadier bez úzkych hrdiel. Najnovšie štandardy HBM3 a HBM3E, ako ich definuje JEDEC Solid State Technology Association, podporujú šírky pásma presahujúce 1 TB/s na zásobník, čo je nevyhnutné na tréning veľkorozmerných neurónových sietí a real-time odvodzovanie v dátových centrách. Tieto rozhrania sú úzko integrované s akcelerátorovými čipmi pomocou pokročilých baliacich techník, ako je 2.5D a 3D integrácia, minimalizujúc stratu signálu a latenciu.

V prostrediach HPC sa využívajú vysoké šírky pásma HBM a energetická efektívnosť na urýchlenie vedeckých simulácií, modelovania financií a iných datovo náročných úloh. Superpočítače, ako tie, ktoré postavili Cray Inc. a Fujitsu Limited, využívajú procesory s HBM na dosiahnutie petaskalových a eksaskalových výkonnostných cieľov. Dizajn rozhrania musí vyriešiť výzvy ako integrita signálu, tepelné riadenie a korekcia chýb na zabezpečenie spoľahlivej prevádzky pri extrémnych pracovných záťažiach.

Zariadenia okrajového výpočtu, ktoré vyžadujú kompaktné formáty a nízku spotrebu energie, tiež začínajú prijímať HBM rozhrania. Spoločnosti ako Samsung Electronics Co., Ltd. a SK hynix Inc. vyvíjajú HBM riešenia prispôsobené pre čipy AI na okraji, vyvažujúc potrebné šírky pásma so prísnymi požiadavkami na energiu a teplo.

Pohľad na rok 2025 naznačuje, že ďalšie zlepšovanie dizajnu HBM rozhraní bude kľúčové na podporu nasledujúcej generácie aplikácií AI, HPC a okrajového výpočtu. Inovácie v balení, signalizácii a architektúrach pamäťových ovládačov posunú ďalej škálovateľnosť a efektívnosť akcelerátorov AI, zabezpečujúc, že pamäťová šírka pásma bude krok pred exponenciálnym rastom výpočtového dopytu.

Analýza dodávateľského reťazca a ekosystému

Dodávateľský reťazec a ekosystém pre dizajn rozhrania s vysokorýchlostnou pamäťou (HBM) v akcelerátoroch AI sa vyznačuje komplexnou sieťou výrobcov polovodičov, dodávateľov pamäte, továren a poskytovateľov návrhových nástrojov. HBM, so svojimi vertikálne stohovanými DRAM čipmi a širokým rozhraním, je kritickým faktorom pre akcelerátory AI, ponúkajúc šírku pásma a energetickú efektívnosť potrebnú pre veľké pracovné zaťaženia strojového učenia. Dizajn a integrácia HBM rozhraní vyžaduje úzku spoluprácu medzi dodávateľmi pamäte, ako sú Samsung Electronics Co., Ltd., Micron Technology, Inc. a SK hynix Inc., a poprednými dizajnérmi čipov AI ako NVIDIA Corporation a Advanced Micro Devices, Inc. (AMD).

Ekosystém je ďalej podporovaný pokročilými technológie balenia a prepojenia, ako sú kremíkové interposery a 2.5D/3D integrácie, poskytované továreňami ako Taiwan Semiconductor Manufacturing Company Limited (TSMC) a Intel Corporation. Tieto továrne umožňujú fyzickú integráciu zásobníkov HBM s logickými čipmi, zabezpečujúc integritu signálu a tepelné riadenie pri vysokých dátových rýchlostiach. Poskytovatelia EDA nástrojov, vrátane Synopsys, Inc. a Cadence Design Systems, Inc., ponúkajú špecializované IP a overovacie riešenia na riešenie prísnych požiadaviek na časovanie, výkon a spoľahlivosť HBM rozhraní.

Úsilie o standardizáciu, vedené organizáciami ako JEDEC Solid State Technology Association, zohráva kľúčovú úlohu pri definovaní špecifikácií rozhrania HBM a zabezpečovaní interoperability naprieč dodávateľským reťazcom. Rýchla evolúcia štandardov HBM (napr. HBM3, HBM3E) si vyžaduje, aby účastníci ekosystému neustále aktualizovali svoje návrhárske procesy a procesy výroby. Okrem toho, rastúci dopyt po akcelerátoroch AI v dátových centrách a okrajových zariadeniach poháňa investície do expanzie kapacity a odolnosti dodávateľského reťazca, čo sa odráža v nedávnych oznámeniach od hlavných partnerov výrobcov pamäte a továreň.

Na záver, ekosystém dizajnu HBM rozhraní pre akcelerátory AI v roku 2025 je charakterizovaný hlbokými závislosťami medzi dodávateľmi pamäte, dizajnérmi čipov, továreňami, dodávateľmi EDA a normotvornými organizáciami. Toto spolupracujúce prostredie je nevyhnutné na dodanie vysokovýkonných a energeticky efektívnych pamäťových subsystémov, ktoré sú základom budúcich pracovných záťaží AI.

Budúci výhľad: Disruptívne technológie a HBM rozhrania novej generácie

Budúcnosť dizajnu rozhrania s vysokorýchlostnou pamäťou (HBM) pre akcelerátory AI je na pokraji významnej transformácie, poháňanej disruptívnymi technológiami a evolúciou štandardov HBM novej generácie. Ako pracovné záťaže AI naďalej vyžadujú vyššiu pamäťovú šírku pásma a nižšiu latenciu, priemysel sa posúva za HBM2E a HBM3 smerom k ešte pokročilejším riešeniam, ako sú HBM3E a raný výskum do HBM4. Tieto nové štandardy sľubujú dodanie bezprecedentných prenosových rýchlostí, pričom HBM3E cieli na rýchlosti až do 9,2 Gbps na pin a celkovú šírku pásma presahujúcu 1,2 TB/s na zásobník, kritický skok pre tréning a odvodzovanie AI na veľkom rozsahu (Samsung Electronics).

Disruptívne technológie rozhraní tiež začínajú chodiť, aby adresovali výzvy integrity signálu, dodávania energie a tepelného riadenia, ktoré sú inherentné pri stohovaní väčších pamäťových čipov a zvyšovaní hustoty I/O. Inovácie ako pokročilé architektúry cez kremíkové viazania (TSV), zlepšené materiály interposera a adopcia dizajnov na báze čipletov umožňujú tesnejšiu integráciu medzi akcelerátormi AI a zásobníkmi HBM. Napríklad použitie kremíkových mostov a organických interposers sa skúma s cieľom znížiť náklady a zlepšiť škálovateľnosť, pričom sa zachová rýchle signálovanie potrebné pre HBM novej generácie (Advanced Micro Devices, Inc.).

Do budúcnosti sa očakáva, že integrácia HBM s emergentnými architektúrami akcelerátorov AI—ako sú tie využívajúce 2.5D a 3D balenie—ďalej rozmaže línie medzi pamäťou a výpočtom. Tento prístup spolubalenia je očakávaný na minimalizáciu pohybu údajov, zníženie spotreby energie a uvoľnenie nových úrovní paralelizmu pre veľké jazykové modely a generatívne pracovné záťaže AI. Priemyselní lídri tiež spolupracujú na nových protokoloch rozhrania a schémach korekcie chýb na zabezpečenie spoľahlivosti a škálovateľnosti pri rastúcich pamäťových šírkach pásma (Micron Technology, Inc.).

Na záver, budúcnosť dizajnu HBM rozhraní pre akcelerátory AI bude formovaná rýchlym pokrokom v technológii pamäte, inováciami balenia a spoludizajnom na systémovej úrovni. Tieto vývojové trendy určia výkonnostné parametre pre hardvér AI v roku 2025 a ďalej, umožňujúc ďalšiu vlnu prelomov v strojovom učení a analýze údajov.

Strategické odporúčania pre zainteresované strany

Keď sa akcelerátory AI čoraz viac spoliehajú na vysokorýchlostnú pamäť (HBM) na splnenie požiadaviek veľkorozmerného strojového učenia a hlbokého učenia, zainteresované strany—vrátane dizajnérov čipov, systémových integrátorov a prevádzkovateľov dátových centier—musia prijať perspektívne stratégie na optimalizáciu dizajnu HBM rozhraní. Nasledujúce odporúčania sú prispôsobené na to, aby adresovali vyvíjajúcu sa krajinu integrácie HBM v hardvéri AI pre rok 2025 a ďalej.

- Uprednostnite spoludizajn pamäte a výpočtu: Spolupráca medzi tímami pamäte a výpočtu je nevyhnutná. Spoločným optimalizovaním HBM rozhrania s architektúrou akcelerátora AI môžu zainteresované strany minimalizovať latenciu a maximalizovať prenos. Spoločnosti ako Samsung Electronics Co., Ltd. a Micron Technology, Inc. preukázali výhody takýchto integrovaných prístupov vo svojich najnovších HBM riešeniach.

- Adoptujte najnovšie štandardy HBM: Udržiavanie kroku s najnovšími štandardmi HBM, ako HBM3 a vznikajúci HBM4, zabezpečuje kompatibilitu a prístup k vyšším šírkam pásma a zlepšenej energetickej efektívnosti. JEDEC Solid State Technology Association pravidelne aktualizuje tieto štandardy a skorá adopcia môže poskytnúť konkurenčnú výhodu.

- Investujte do pokročilých baliacich technológií: 2.5D a 3D integrácia, ako sú kremíkové interposery a cez kremíkové viazania (TSV), sú kritické pre efektívny dizajn HBM rozhraní. Spolupráca s odborníkmi na balenie, ako je Taiwan Semiconductor Manufacturing Company Limited (TSMC), môže pomôcť zainteresovaným stranám využívať špičkové riešenia prepojenia.

- Optimalizujte dodávanie energie a tepelné riadenie: Ako HBM zásobníky rastú v hustote a rýchlosti, dodávanie energie a odvod tepla sa stávajú náročnejšími. Zainteresované strany by mali investovať do pokročilých IC riadenia energie a inovatívnych riešení chladenia, spolupracujúc s partnermi ako CoolIT Systems Inc. pre tepelné riadenie.

- Podporujte spoluprácu v ekosystéme: Zapojenie do priemyselných spolkov a normotvorných organizácií, ako je OIF (Optical Internetworking Forum), môže pomôcť zainteresovaným stranám zostať informovanými o inováciách rozhraní a požiadavkách na interoperabilitu.

Implementáciou týchto strategických odporúčaní môžu zainteresované strany zabezpečiť, že ich dizajny HBM rozhraní pre akcelerátory AI zostanú robustné, škálovateľné a pripravené na budúcnosť, podporujúc nasledujúcu generáciu pracovných záťaží AI.

Zdroje a odkazy

- Micron Technology, Inc.

- NVIDIA Corporation

- JEDEC Solid State Technology Association

- Amkor Technology, Inc.

- Cray Inc.

- Fujitsu Limited

- Synopsys, Inc.

- OIF (Optical Internetworking Forum)