Odemykání síly vysokorychlostní paměti: Jak návrh HBM rozhraní revolucionalizuje AI akcelerátory v roce 2025 a dále. Prozkoumejte technologie, růst trhu a strategické příležitosti, které formují novou éru AI hardwaru.

- Výkonný souhrn: Klíčové poznatky a strategické poznatky

- Přehled trhu: Návrh HBM rozhraní pro AI akcelerátory v roce 2025

- Technologická krajina: Vývoj standardů a architektur HBM

- Konkurenční analýza: Vedoucí hráči a trendy inovací

- Velikost trhu a prognóza (2025–2030): CAGR, projekce příjmů a regionální rozdělení

- Faktory a výzvy: Požadavky na výkon, energetická účinnost a složitosti integrace

- Novo vznikající aplikace: AI, HPC, datová centra a okrajové výpočty

- Analýza dodavatelského řetězce a ekosystému

- Budoucí výhled: Disruptivní technologie a akcelerátory HBM nové generace

- Strategická doporučení pro zúčastněné strany

- Zdroje a odkazy

Výkonný souhrn: Klíčové poznatky a strategické poznatky

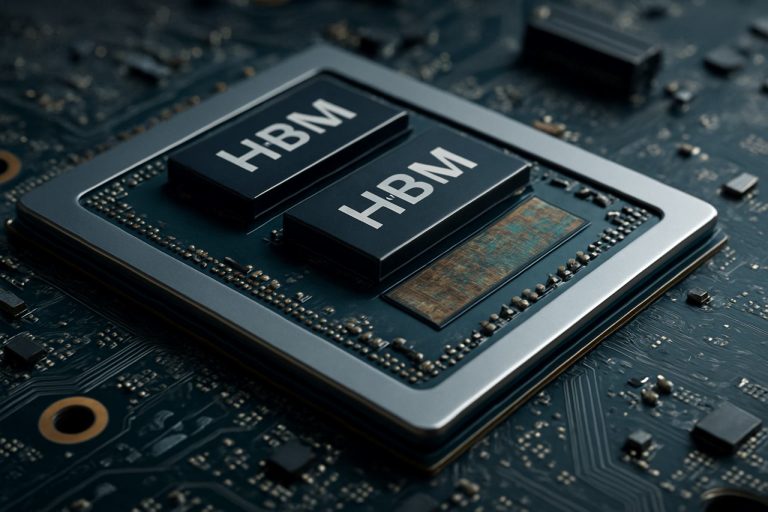

Návrh HBM rozhraní se stal klíčovým prvkem pro akcelerátory AI nové generace, které čelí rostoucím požadavkům na šířku pásma paměti, energetickou účinnost a kompaktní formát v datově intenzivních aplikacích. V roce 2025 rychlý vývoj pracovních zátěží AI—zejména v oblasti hlubokého učení a velkých jazykových modelů—zesílil potřebu paměťových řešení, která mohou dodávat terabajty za sekundu šířky pásma při minimalizaci latence a spotřeby energie. HBM, se svou 3D architekturou a technologií přesilikonových přesunů (TSV), se stala preferovaným paměťovým rozhraním pro přední dodavatele AI akcelerátorů.

Klíčové poznatky naznačují, že přijetí HBM3 a očekávané zavedení HBM4 nastavují nová měřítka ve šířce pásma, přičemž HBM3 nabízí až 819 GB/s na zásobník a HBM4 se očekává, že překročí 1 TB/s. Tyto pokroky umožňují AI akcelerátorům zpracovávat větší datové sady v reálném čase, což významně zlepšuje propustnost trénování a inferenčního procesu. Hlavní hráči v tomto odvětví, jako jsou Samsung Electronics Co., Ltd., Micron Technology, Inc. a SK hynix Inc., jsou v čele inovací HBM a úzce spolupracují s návrháři AI hardwaru na optimalizaci rozhraní protokolů a integrity signálu.

Strategické poznatky odhalují, že úspěšný návrh HBM rozhraní závisí na několika faktorech: pokročilých balících technikách (jako je 2.5D a 3D integrace), robustním tepelné managementu a ko-designu paměťových řadičů s procesorovými jádry AI. Společnosti jako Advanced Micro Devices, Inc. a NVIDIA Corporation využívají tyto strategie k dodání AI akcelerátorů s bezprecedentními metrikami výkonnosti na watt. Dále se zvyšuje integrace HBM s architekturami založenými na chipletech, což nabízí modularitu a škálovatelnost pro budoucí AI systémy.

Vzhledem k budoucnosti se očekává, že ekosystém HBM rozhraní bude těžit z úsilí o standardizaci vedeného organizacemi jako JEDEC Solid State Technology Association, které zjednodušují interoperabilitu a zrychlují uvedení nových paměťových řešení na trh. Jak se modely AI i nadále rozrůstají v komplexnosti, strategická shoda návrhu HBM rozhraní s vyvíjejícími se pracovním zátěžemi AI bude nezbytná pro udržení konkurenční výhody v krajině AI hardwaru.

Přehled trhu: Návrh HBM rozhraní pro AI akcelerátory v roce 2025

Trh návrhu rozhraní vysokorychlostní paměti (HBM) pro AI akcelerátory je připraven na významný růst v roce 2025, poháněn rostoucími výpočetními požadavky umělé inteligence a pracovními zátěžemi strojového učení. HBM, technologie DRAM s vertikálním stohováním, nabízí značná zlepšení šířky pásma paměti a energetické účinnosti ve srovnání s tradičními paměťovými řešeními, což z ní činí kritického aktéra pro akcelerátory AI nové generace.

V roce 2025 urychluje přijetí HBM rozhraní přední polovodičové společnosti a provozovatelé hyperškálových datových center, kteří se snaží překonat paměťové úzké hrdlo inherentní v úlohách trénování a inference AI. Nejnovější standardy HBM, jako HBM3 a vyvíjející se HBM3E, dodávají šířky pásma přesahující 1 TB/s na zařízení, což podporuje paralelní zpracování požadavků velkých jazykových modelů a generativních AI systémů. Společnosti jako Samsung Electronics Co., Ltd., Micron Technology, Inc. a SK hynix Inc. jsou v čele vývoje HBM a dodávají paměťová řešení, která se rychle integrují do návrhu AI akcelerátorů.

Návrh rozhraní pro HBM v AI akcelerátorech je stále složitější, vyžadující pokročilé balicí technologie, jako je 2.5D a 3D integrace. Tyto přístupy umožňují blízkou fyzickou blízkost HBM stohů k výpočetním jednotkám, což minimalizuje latenci a maximalizuje průchod dat. Polovodičové výrobny jako Taiwan Semiconductor Manufacturing Company Limited (TSMC) a Intel Corporation investují do pokročilých řešení pro mezikus a balení na podporu těchto architektur.

Pop demands for HBM-enabled AI akcelerátory jsou obzvlášť silné v cloudových datových centrech, okrajovém výpočtu a sektorech vysokovýkonného výpočtu (HPC). Hlavní dodavatelé AI čipů, včetně NVIDIA Corporation a Advanced Micro Devices, Inc. (AMD), integrují HBM do svých vlajkových produktů, aby dodali šířku pásma paměti potřebnou pro nejmodernější AI modely. Konkurenční krajina je dále formována vyvíjejícími se standardy od organizací jako JEDEC Solid State Technology Association, které nadále definují nové specifikace HBM, aby splnily budoucí požadavky AI.

Celkově je trh návrhu HBM rozhraní pro AI akcelerátory v roce 2025 charakterizován rychlými inovacemi, strategickými partnerstvími v rámci dodavatelského řetězce polovodičů a neúprosním zaměřením na šířku pásma, energetickou účinnost a škálovatelnost na podporu nové vlny pokroků v AI.

Technologická krajina: Vývoj standardů a architektur HBM

Technologická krajina návrhu vysokorychlostní paměti (HBM) se rychle vyvíjela, aby splnila rostoucí požadavky akcelerátorů AI. Od svého zavedení prošla HBM několika generacemi vylepšení, přičemž každá iterace přinášela vyšší šířku pásma, zvýšenou kapacitu a vylepšenou energetickou účinnost. První standard HBM, vyvinutý společnostmi Samsung Electronics Co., Ltd. a SK hynix Inc. ve spolupráci s Advanced Micro Devices, Inc. (AMD), nastavil scénu pro vertikální stohování DRAM čipů a jejich propojení pomocí přesilikonových průchodů (TSV), což umožnilo široké I/O a nízkou spotřebu energie.

Standardy HBM2 a HBM2E, ratifikované JEDEC Solid State Technology Association, dále zvýšily šířku pásma a kapacitu na zásobník, podporující až 3.6 Gbps na pin a 16 GB na zásobník. Tato vylepšení byla kritická pro akcelerátory AI, které vyžadují rychlý přístup k velkým datovým sadám a modelům. Nejnovější standard HBM3, představený v roce 2022, posunuje šířku pásma na více než 6.4 Gbps na pin a kapacity zásobníků až na 24 GB, přičemž Micron Technology, Inc. a SK hynix Inc. jsou mezi prvními, kteří oznámili produkty HBM3. HBM3E, jehož široké přijetí se očekává v roce 2025, by mělo přinést ještě vyšší rychlosti a vylepšené tepelné řízení, aby vyhovělo potřebám pracovních zátěží AI nové generace.

Architektonicky se integrace HBM s akcelerátory AI posunula od tradičního umístění vedle sebe na PCB k 2.5D a 3D balení, jako jsou silikónové mezikusy a pokročilé návrhy chipletů. NVIDIA Corporation a AMD byly průkopníky využití HBM ve svých GPU a AI akcelerátorech, přičemž využívají tyto balicí techniky k minimalizaci ztráty signálu a maximalizaci šířky pásma paměti. Přijetí ko-balených optik a paměťových řadičů na čipu se také objevuje, což dále snižuje latenci a spotřebu energie.

Pohled směrem k roku 2025 je charakterizován soustředěním na škálovatelnost, energetickou účinnost a flexibilitu integrace. Vedoucí průmysloví hráči spolupracují na nových standardech a referenčních architekturách, aby zajistili interoperabilitu a podpořili exponenciální růst velikosti a složitosti AI modelů. Jak akcelerátory AI nadále posunují hranice výkonu, vývoj standardů a architektur HBM zůstává základním kamenem inovace v tomto oboru.

Konkurenční analýza: Vedoucí hráči a trendy inovací

Konkurenční krajina návrhu vysokorychlostní paměti (HBM) v AI akcelerátorech se rychle vyvíjí v důsledku rostoucích požadavků pracovních zátěží umělé inteligence a potřeby efektivního, vysokorychlostního přenosu dat mezi pamětí a výpočetními jednotkami. Klíčoví hráči v tomto odvětví, jako jsou Samsung Electronics Co., Ltd., Micron Technology, Inc. a SK hynix Inc., dominují sektoru výroby HBM, kteří každý představují po sobě jdoucí generace HBM (HBM2E, HBM3 a dále) s vyšší šířkou pásma, kapacitou a energetickou účinností.

Na frontě AI akcelerátorů společnosti jako NVIDIA Corporation a Advanced Micro Devices, Inc. (AMD) integrovaly HBM do svých vlajkových GPU a akcelerátorů datových center, využívající širokého rozhraní paměti a 3D stohování k minimalizaci úzkých míst v aplikacích hlubokého učení a vysokovýkonného výpočtu. Intel Corporation také přijala HBM ve svých AI a HPC produktech, zaměřujícím se na optimalizaci rozhraní pro nižší latenci a vyšší propustnost.

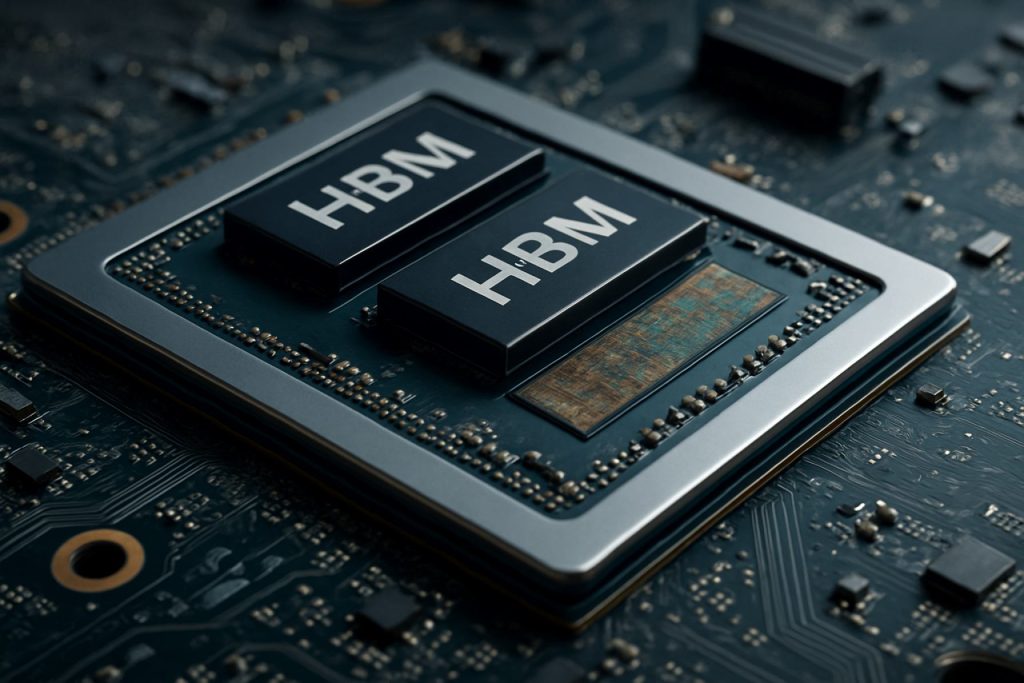

Trendy inovací v návrhu HBM rozhraní se soustředí na maximalizaci šířky pásma při redukci spotřeby energie a fyzického rozsahu. Techniky, jako jsou pokročilé přesilikonové vazebné (TSV) architektury, zlepšená integrita signálu a dynamické řízení napětí/frekvence, se implementují k vyřešení těchto výzev. Přijetí HBM3 a vývoj standardů HBM4, vedené JEDEC Solid State Technology Association, posouvají hranice paměťové šířky pásma, přičemž HBM3 cílí na rychlosti přesahující 800 GB/s na zásobník a HBM4 se očekává, že tuto hodnotu významně překročí.

Dalším pozoruhodným trendem je ko-balení HBM s AI akcelerátory pomocí pokročilých balicích technologií, jako je 2.5D a 3D integrace. Taiwan Semiconductor Manufacturing Company Limited (TSMC) a Amkor Technology, Inc. jsou v čele poskytování těchto balicích řešení, což umožňuje bližší integraci a vylepšené tepelné řízení. Tento přístup ko-designu je kritický pro systémy AI nové generace, kde šířka pásma paměti a blízkost k výpočetním jednotkám přímo ovlivňuje výkon a účinnost.

Shrnuto, konkurenční dynamika v návrhu HBM rozhraní pro AI akcelerátory je formována rychlými inovacemi, strategickými partnerstvími mezi výrobci pamětí a čipů a neúprosním úsilím o dosažení vyšší šířky pásma a nízkých energetických řešení k uspokojení potřeb AI-založených pracovních zátěží.

Velikost trhu a prognóza (2025–2030): CAGR, projekce příjmů a regionální rozdělení

Trh pro návrh HBM rozhraní v AI akcelerátorech je připraven na silný růst v letech 2025 až 2030, poháněný rostoucími požadavky na vysokovýkonný výpočet v oblasti umělé inteligence, strojového učení a aplikací datových center. Globální trh HBM rozhraní se očekává, že dosáhne složeného ročního indexu růstu (CAGR) přibližně 25–30 % během tohoto období, což odráží rychlé přijetí HBM-enabled AI akcelerátorů ve firemním a cloudovém prostředí.

Očekávané příjmy naznačují, že velikost trhu, která v roce 2025 bude oceněna na přibližně 2.5 miliardy USD, by mohla překročit 7.5 miliardy USD do roku 2030. Tento nárůst je připisován rostoucí integraci HBM v čipech AI nové generace, které vyžadují ultrarychlá paměťová rozhraní pro zpracování obrovských paralelních výpočetních pracovních zátěží. Klíčoví hráči v tomto odvětví, jako jsou Samsung Electronics Co., Ltd., Micron Technology, Inc. a SK hynix Inc., investují značné prostředky do výzkumu a vývoje, aby pokročili v technologiích HBM rozhraní, což dále urychluje expanzi trhu.

Regionálně se očekává, že Asie a Tichomoří budou dominovat trhu návrhu HBM rozhraní, přičemž do roku 2030 zaujmou více než 45 % globálních příjmů. Tato dominance je podložena přítomností hlavních výrobců polovodičů a výrobců pamětí v zemích, jako jsou Jižní Korea, Tchaj-wan a Čína. Severní Amerika se stejnak přiblíží, poháněna koncentrací vývojářů AI akcelerátorů a hyperskalových datových center ve Spojených státech a Kanadě. Evropa také zaznamenává stabilní růst, zejména v sektorech automobilové AI a průmyslové automatizace.

Proliferace aplikací řízených AI v okrajovém výpočtu, autonomních vozidlech a vysokofrekvenčním obchodování dále urychluje přijetí pokročilých HBM rozhraní. Jak se modely AI stávají složitějšími a datově náročnějšími, potřeba vyšší šířky pásma paměti a nižší latence tlačí návrháře čipů k přijetí standardů HBM2E, HBM3 a nově se objevujících standardů HBM4, které definuje JEDEC Solid State Technology Association.

Celkově bude trh návrhu HBM rozhraní pro AI akcelerátory do roku 2030 čelit významné expanze, s výrazným regionálním růstem v oblasti Asie a Tichomoří a Severní Ameriky a jasným trendem směrem k vyšší šířce pásma a energeticky účinnějším paměťovým řešením.

Faktory a výzvy: Požadavky na výkon, energetická účinnost a složitosti integrace

Rychlý vývoj pracovních zátěží umělé inteligence (AI) dal předem nevídané požadavky na paměťové subsystémy, což činí vysokorychlostní paměť (HBM) kritickým aktérem pro akcelerátory AI nové generace. Návrh HBM rozhraní musí řešit několik klíčových faktorů a výzev, zejména v oblastech výkonu, energetické účinnosti a složitosti integrace.

Požadavky na výkon: AI akcelerátory vyžadují masivní šířku pásma paměti, aby zásobily datově náročné výpočetní jednotky, zejména pro modely hlubokého učení s miliardami parametrů. HBM, se svou 3D architekturou a širokým I/O, nabízí šířky pásma přesahující 1 TB/s v nejnovějších generacích. Nicméně dosažení těchto hodnot v praxi vyžaduje pečlivý návrh rozhraní, aby se minimalizovala latence, maximalizoval propustnost a zajistila se integrita signálu při vysokých datech. Rozhraní musí také podporovat efektivní vzory pohybu dat typické pro pracovní zátěže AI, jako jsou velké matice násobení a tenzory operací, které vytvářejí dodatečné zatížení paměťových řadičů a interkonexí.

Energetická účinnost: S rostoucími nároky na AI akcelerátory se spotřeba energie stává kritickým omezením, a to jak pro nasazení v datových centrech, tak i pro aplikace na okraji. Blízkost HBM k procesoru a její použití přesilikonových vazeb (TSV) snižují energii na bit ve srovnání s tradiční pamětí DDR. Nicméně návrh rozhraní musí dále optimalizovat výkon pomocí pokročilých signalizačních technik, dynamického řízení napětí a frekvence a inteligentního řízení výkonu. Vyvážení vysoké šířky pásma s nízkým energetickým provozem je trvalou výzvou, zejména pokud se paměťové stohy zvětšují na kapacitě a rychlosti. Organizace jako Samsung Electronics Co., Ltd. a Micron Technology, Inc. aktivně vyvíjí nové generace HBM s vylepšenou energetickou účinností.

Složitosti integrace: Integrace HBM s AI akcelerátory zahrnuje významné balicí a systémové výzvy. Fyzické stohování paměťových čipů a jejich propojení s procesorem prostřednictvím silikónových mezikusů nebo pokročilých substrátů vyžaduje přesnou výrobu a tepelné řízení. Integrita signálu, elektromagnetické rušení a mechanický stres musí být všechna řešena, aby se zajistila spolehlivá činnost. Dále musí být rozhraní kompatibilní s vyvíjejícími se standardy, jako jsou ty definované JEDEC Solid State Technology Association, aby se zajistila interoperabilita a budoucí škálovatelnost. Složitost se zvyšuje, jak akcelerátory přejímají architektury založené na chipletech, což vyžaduje robustní HBM řešení, která mohou podporovat heterogenní integraci.

Celkově je návrh HBM rozhraní pro AI akcelerátory v roce 2025 formován potřebou dodávat extrémní šířku pásma, udržet energetickou účinnost a řídit složitosti pokročilé integrace, a to vše při zachování tempa s rychlými inovacemi v AI hardwaru.

Novo vznikající aplikace: AI, HPC, datová centra a okrajové výpočty

Rychlá evoluce umělé inteligence (AI), vysokovýkonného výpočtu (HPC), datových center a okrajového výpočtu vytváří bezprecedentní poptávku po šířce pásma a účinnosti paměti. Návrh rozhraní HBM se stal klíčovou technologií pro AI akcelerátory, umožňující obrovské paralelní zpracování a propustnost dat vyžadovanou moderními pracovními zátěžemi hlubokého učení a analýzy dat. HBM toho dosahuje stohováním více DRAM čipů vertikálně a jejich propojením pomocí přesilikonových průchodů (TSV), což vede k výrazně vyšší šířce pásma a nižší spotřebě energie ve srovnání s tradičními paměťovými rozhraními.

V AI akcelerátorech, jako jsou ty vyvinuté společnostmi NVIDIA Corporation a Advanced Micro Devices, Inc. (AMD), jsou HBM rozhraní kritická pro zásobování dat miliony procesorových jader bez úzkých míst. Nejnovější standardy HBM3 a HBM3E, jak definuje JEDEC Solid State Technology Association, podporují šířky pásma přesahující 1 TB/s na zásobník, což je nezbytné pro trénink rozsáhlých neuronových sítí a reálnou inference v datových centrech. Tato rozhraní jsou těsně integrována s jádrem akcelerátoru pomocí pokročilých balicích technik, jako je 2.5D a 3D integrace, minimalizující ztrátu signálu a latenci.

V prostředí HPC se vysoká šířka pásma a energetická účinnost HBM využívají k urychlení vědeckých simulací, finančního modelování a dalších datově náročných úloh. Superpočítače, jako ty, které staví Cray Inc. a Fujitsu Limited, využívají procesory s HBM k dosažení cílů petascale a exascale výkonu. Návrh rozhraní musí řešit výzvy, jako je integrita signálu, tepelné řízení a korekce chyb, aby zajistil spolehlivý výkon pod extrémními zátěžemi.

Zařízení okrajového výpočtu, která vyžadují kompaktní formáty a nízkou spotřebu energie, také začínají přijímat HBM rozhraní. Společnosti jako Samsung Electronics Co., Ltd. a SK hynix Inc. vyvíjejí HBM řešení přizpůsobená pro AI čipy na okraji, vyvažující potřeby šířky pásma s přísnými energetickými a tepelnými omezeními.

Pohled směrem k roku 2025 bude pokračující zdokonalování návrhu HBM rozhraní klíčové pro podporu příští generace AI, HPC a okrajových aplikací. Inovace v balení, signalizaci a architekturách paměťových řadičů dále vylepší škálovatelnost a efektivitu AI akcelerátorů, což zajistí, že šířka pásma paměti udrží krok s exponenciálním růstem výpočetních požadavků.

Analýza dodavatelského řetězce a ekosystému

Dodavatelský řetězec a ekosystém návrhu HBM rozhraní pro AI akcelerátory je charakterizován složitou sítí výrobců polovodičů, dodavatelů pamětí, výrobních závodů a poskytovatelů návrhových nástrojů. HBM, se svými vertikálně stohovanými DRAM čipy a širokým rozhraním, je kritickým aktérem pro AI akcelerátory, poskytující šířku pásma a energetickou účinnost vyžadované pro velké úlohy strojového učení. Návrh a integrace HBM rozhraní vyžadují úzkou spolupráci mezi dodavateli pamětí, jako jsou Samsung Electronics Co., Ltd., Micron Technology, Inc. a SK hynix Inc., a předními návrháři AI čipů, jako jsou NVIDIA Corporation a Advanced Micro Devices, Inc. (AMD).

Ekosystém je dále podporován pokročilými balicími a mezikusemi, jako jsou silikónové mezikusy a integrace 2.5D/3D, poskytované výrobními podniky jako Taiwan Semiconductor Manufacturing Company Limited (TSMC) a Intel Corporation. Tyto výrobny umožňují fyzickou integraci stohů HBM s logickými čipy, čímž zajišťují integritu signálu a tepelné řízení při vysokých datových rychlostech. Poskytovatelé EDA nástrojů, včetně Synopsys, Inc. a Cadence Design Systems, Inc., nabízejí specializovaná IP a ověřovací řešení, aby splnily přísné požadavky na časování, energetický výkon a spolehlivost HBM rozhraní.

Úsilí o standardizaci, vedené organizacemi jako JEDEC Solid State Technology Association, hraje klíčovou roli při definování specifikací HBM rozhraní a zajištění interoperability po celém dodavatelském řetězci. Rychlý vývoj standardů HBM (např. HBM3, HBM3E) vyžaduje, aby účastníci ekosystému průběžně aktualizovali své návrhové procesy a výrobní postupy. Dále rostoucí poptávka po AI akcelerátorech v datových centrech a okrajových zařízeních podporuje investice do expanze kapacity a odolnosti dodavatelského řetězce, což se projevuje v nedávných oznámeních od hlavních partnerů paměti a výrobních závodů.

Celkově je ekosystém návrhu HBM rozhraní pro AI akcelerátory v roce 2025 poznamenán hlubokými vzájemnými závislostmi mezi dodavateli pamětí, návrháři čipů, výrobními podniky, dodavateli EDA a standardizačními orgány. Toto spolupráce je klíčová pro dodání vysoce výkonných, energeticky účinných paměťových subsystémů, které tvoří základ pracovních zátěží AI nové generace.

Budoucí výhled: Disruptivní technologie a akcelerátory HBM nové generace

Budoucnost návrhu HBM rozhraní pro AI akcelerátory je připravena na významnou transformaci, poháněnou disruptivními technologiemi a evolucí standardů HBM nové generace. Jak pracovní zátěže AI i nadále vyžadují vyšší šířku pásma paměti a nižší latenci, průmysl se posouvá za standardy HBM2E a HBM3 směrem k ještě pokročilejším řešením, jako je HBM3E a raný výzkum HBM4. Tyto nové standardy slibují dodání bezprecedentních datových rychlostí, přičemž HBM3E cílí na rychlosti až 9.2 Gbps na pin a celkové šířky pásma přes 1.2 TB/s na zásobník, což představuje kritický skok v trénování a inference AI v měřítku (Samsung Electronics).

Disruptivní technologie rozhraní se také objevují k řešení problémů s integritou signálu, dodávkou energie a tepelným řízením, které jsou inherentní při stohování více paměťových čipů a zvyšování hustoty I/O. Inovace, jako jsou pokročilé architektury přes silikónové vazebné (TSV), zlepšené mezikusové materiály a přijetí návrhů založených na chipletu, umožňují těsnější integraci mezi AI akcelerátory a stohy HBM. Například použití silikónových mostů a organických mezikusů se zkoumá za účelem snížení nákladů a zlepšení škálovatelnosti, přičemž se zachovává vysokorychlostní signalizace požadovaná pro příští generaci HBM (Advanced Micro Devices, Inc.).

Dále integrace HBM s nově vznikajícími architekturami AI akcelerátorů—jako jsou ty, které využívají balení 2.5D a 3D—je očekávána, že dále rozmaže hranice mezi pamětí a výpočtem. Tento přístup ko-balení by měl minimalizovat pohyb dat, snížit spotřebu energie a odemknout nové úrovně paralelismu pro velké jazykové modely a generativní AI pracovní zátěže. Průmysloví lídři také spolupracují na nových protokolech pro signalizaci a schématech korekce chyb, aby zajistili spolehlivost a škálovatelnost při prudkém vzrůstu šířky pásma paměti (Micron Technology, Inc.).

Shrnuto, budoucnost návrhu HBM rozhraní pro AI akcelerátory bude formována rychlým pokrokem v technologii paměti, inovací v balení a ko-designem na úrovni systémů. Tyto vývoje mají potenciál redefinovat výkonnostní možnosti pro AI hardware v roce 2025 a dál, umožňující další vlnu průlomů v oblasti strojového učení a datové analýzy.

Strategická doporučení pro zúčastněné strany

Jak AI akcelerátory stále více spoléhají na vysokorychlostní paměť (HBM) k uspokojení požadavků velkých strojového učení a hlubokého učení, zúčastněné strany—včetně návrhářů čipů, systémových integrátorů a provozovatelů datových center—by měly přijmout vyhlídky do budoucnosti, aby optimalizovaly návrh HBM rozhraní. Následující doporučení jsou navržena tak, aby reagovala na vyvíjející se krajinu integrace HBM v AI hardwaru pro rok 2025 a dále.

- Prioritizujte ko-design paměti a výpočtu: Spolupráce mezi týmy paměti a výpočtu je nezbytná. Kooptimalizací HBM rozhraní ve spojení s architekturou AI akcelerátoru mohou zúčastněné strany minimalizovat latenci a maximalizovat propustnost. Společnosti jako Samsung Electronics Co., Ltd. a Micron Technology, Inc. prokázaly výhody takových integrovaných přístupů ve svých nejnovějších řešeních HBM.

- Přijměte nejnovější standardy HBM: Držení se aktuálních nejnovějších standardů HBM, jako jsou HBM3 a vyvíjející se HBM4, zajišťuje kompatibilitu a přístup k vyšším šířkám pásma a vylepšené energetické účinnosti. JEDEC Solid State Technology Association pravidelně aktualizuje tyto standardy a včasné přijetí může poskytnout konkurenční výhodu.

- Investujte do pokročilých balicích technologií: 2.5D a 3D integrace, jako jsou silikónové mezikusy a přesilikonové vazby (TSV), jsou kritické pro efektivní návrh HBM rozhraní. Spolupráce s balicími specialisty, jako je Taiwan Semiconductor Manufacturing Company Limited (TSMC), může zúčastněným stranám pomoci využít špičková řešení pro interkonektivitu.

- Optimalizujte dodávky výkonu a tepelné řízení: Jak se HBM stohy zvyšují na hustotě a rychlosti, dodávky výkonu a odvod tepla se stávají náročnějšími. Zúčastněné strany by měly investovat do pokročilých IC pro řízení výkonu a inovativních řešení chlazení, spolupracující s partnery, jako je CoolIT Systems Inc. pro tepelné řízení.

- Podporujte spolupráci ekosystému: Angažování se v průmyslových konsorciích a standardizačních orgánech, jako je OIF (Optical Internetworking Forum), může zúčastněným stranám pomoci zůstat informovaní o inovacích rozhraní a požadavcích na interoperabilitu.

Implementací těchto strategických doporučení mohou zúčastněné strany zajistit, aby jejich návrhy HBM rozhraní pro AI akcelerátory zůstaly robustní, škálovatelné a připravené na budoucnost, s podporou další generace pracovních zátěží AI.

Zdroje a odkazy

- Micron Technology, Inc.

- NVIDIA Corporation

- JEDEC Solid State Technology Association

- Amkor Technology, Inc.

- Cray Inc.

- Fujitsu Limited

- Synopsys, Inc.

- OIF (Optical Internetworking Forum)