De Kracht van High-Bandwidth Memory Ontgrendelen: Hoe HBM Interface Ontwerp AI Accelerators Revolutie Brengt in 2025 en Verder. Verken de Technologieën, Marktgroei en Strategische Kansen die de Volgende Era van AI Hardware Vormgeven.

- Executieve Samenvatting: Belangrijkste Bevindingen en Strategische Inzichten

- Marktoverzicht: HBM Interface Ontwerp voor AI Accelerators in 2025

- Technologisch Landschap: Evolutie van HBM-standaarden en Architecturen

- Concurrentieanalyse: Voornaamste Spelers en Innovatietrends

- Marktomvang en Vooruitzichten (2025–2030): CAGR, Omzetprojecties en Regionale Verdeling

- Aandrijvers en Uitdagingen: Prestatie-eisen, Energie-efficiëntie en Integratiecomplexiteit

- Opkomende Toepassingen: AI, HPC, Datacenters en Edge Computing

- Analyse van de Leveringsketen en Ecosysteem

- Toekomstige Vooruitzichten: Ontwrichtende Technologieën en Volgende Generatie HBM Interfaces

- Strategische Aanbevelingen voor Belanghebbenden

- Bronnen & Referenties

Executieve Samenvatting: Belangrijkste Bevindingen en Strategische Inzichten

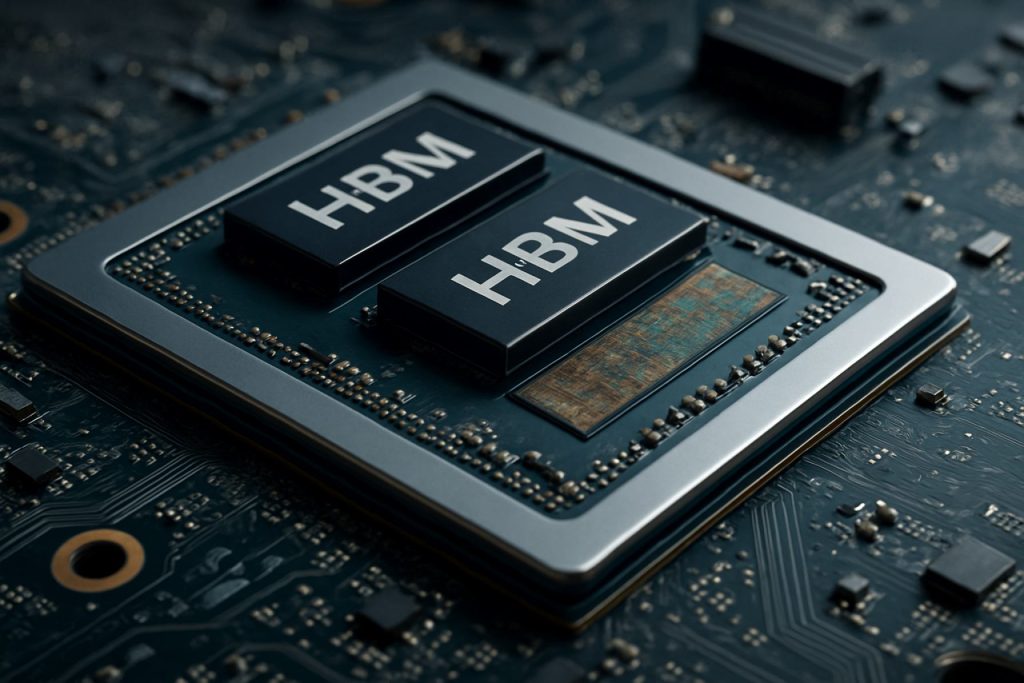

High-Bandwidth Memory (HBM) interface ontwerp is naar voren gekomen als een cruciale factor voor next-generation AI accelerators, waarbij het inspeelt op de toenemende eisen voor geheugendoorvoer, energie-efficiëntie en compacte formaten in data-intensieve toepassingen. In 2025 heeft de snelle evolutie van AI-werklasten – vooral in deep learning en grote taalmodellen – de behoefte aan geheugensystemen die terabytes per seconde bandwidth kunnen leveren, terwijl de latentie en het energieverbruik tot een minimum worden beperkt, verder versterkt. HBM, met zijn 3D-gestapelde architectuur en through-silicon via (TSV) technologie, is de voorkeur geheugensinterface geworden voor toonaangevende verkopers van AI-accelerators.

Belangrijke bevindingen geven aan dat de adoptie van HBM3 en de verwachte uitrol van HBM4 nieuwe normen in de doorvoer vaststellen, met HBM3 die tot 819 GB/s per stap biedt en HBM4 die naar verwachting meer dan 1 TB/s zal overschrijden. Deze vooruitgangen stellen AI-accelerators in staat om grotere datasets in real-time te verwerken, wat de training en inferentie doorvoer aanzienlijk verbetert. Grote spelers in de industrie zoals Samsung Electronics Co., Ltd., Micron Technology, Inc., en SK hynix Inc. zijn vooroplopen in HBM-innovatie en werken nauw samen met ontwerpers van AI-hardware om interfaceprotocollen en signaalintegriteit te optimaliseren.

Strategische inzichten onthullen dat succesvol HBM-interfaceontwerp afhangt van verschillende factoren: geavanceerde verpakkings technieken (zoals 2.5D en 3D integratie), robuuste thermische beheersystemen, en de gezamenlijke ontwikkeling van geheugencamera’s met AI-verwerkingskernen. Bedrijven zoals Advanced Micro Devices, Inc. en NVIDIA Corporation benutten deze strategieën om AI-accelerators te leveren met ongekende prestaties-per-watt metrics. Bovendien wint de integratie van HBM met chiplet-gebaseerde architecturen aan terrein, wat modulariteit en schaalbaarheid biedt voor toekomstige AI-systemen.

Als we vooruitkijken, wordt verwacht dat het HBM-interface-ecosysteem zal profiteren van standaardisatie-inspanningen die worden geleid door organisaties zoals de JEDEC Solid State Technology Association, die de interoperabiliteit stroomlijnen en de tijd naar de markt voor nieuwe geheugensystemen versnellen. Naarmate AI-modellen complexer worden, zal de strategische afstemming van HBM-interfaceontwerp met evoluerende AI-werklasten essentieel zijn om een concurrentievoordeel in het landschap van AI-hardware te behouden.

Marktoverzicht: HBM Interface Ontwerp voor AI Accelerators in 2025

De markt voor High-Bandwidth Memory (HBM) interface ontwerp in AI-accelerators staat op het punt aanzienlijke groei te ondergaan in 2025, gedreven door de toenemende computationele eisen van kunstmatige intelligentie en machine learning werklasten. HBM, een 3D-gestapelde DRAM-technologie, biedt aanzienlijke verbeteringen in geheugendoorvoer en energie-efficiëntie in vergelijking met traditionele geheugensystemen, waardoor het een cruciale enabler is voor de volgende generatie AI-accelerators.

In 2025 wordt de adoptie van HBM-interfaces versneld door toonaangevende halfgeleiderbedrijven en hyperscale datacenteroperators die proberen de geheugenkruiswerkingen inherent aan AI-trainings- en inferentietaken te overwinnen. De laatste HBM-standaarden, zoals HBM3 en de opkomende HBM3E, leveren doorvoeren die meer dan 1 TB/s per apparaat overschrijden, wat de parallelle verwerkingsvereisten van grote taalmodellen en generatieve AI-systemen ondersteunt. Bedrijven zoals Samsung Electronics Co., Ltd., Micron Technology, Inc., en SK hynix Inc. staan voorop in de ontwikkeling van HBM en leveren geheugensystemen die snel worden geïntegreerd in ontwerpen van AI-accelerators.

Het interfaceontwerp voor HBM in AI accelerators wordt steeds complexer en vereist geavanceerde verpakkings technologieën zoals 2.5D en 3D integratie. Deze benaderingen maken de nauwkeurige fysieke nabijheid van HBM-stacks tot verwerkings eenheden mogelijk, waardoor de latentie wordt geminimaliseerd en de gegevensdoorvoer wordt gemaximaliseerd. Halfgeleiderfabrieken zoals Taiwan Semiconductor Manufacturing Company Limited (TSMC) en Intel Corporation investeren in geavanceerde interposer- en verpakkingsoplossingen om deze architecturen te ondersteunen.

De vraag naar HBM-geconfigureerde AI-accelerators is bijzonder sterk in cloud datacenters, edge computing en high-performance computing (HPC) sectoren. Belangrijke AI-chip verkopers, waaronder NVIDIA Corporation en Advanced Micro Devices, Inc. (AMD), integreren HBM in hun vlaggenschipproducten om de geheugendoorvoer die nodig is voor de state-of-the-art AI-modellen te leveren. Het competitieve landschap wordt verder beïnvloed door evoluerende normen van organisaties zoals de JEDEC Solid State Technology Association, die blijven definiëren welke nieuwe HBM-specificaties aan toekomstige AI-eisen voldoen.

Al met al wordt de HBM-interfaceontwerp markt voor AI-accelerators in 2025 gekenmerkt door snelle innovatie, strategische partnerschappen in de halfgeleider leveringsketen, en een voortdurende focus op doorvoer, energie-efficiëntie en schaalbaarheid ter ondersteuning van de volgende golf van AI-vooruitgangen.

Technologisch Landschap: Evolutie van HBM-standaarden en Architecturen

Het technologische landschap voor High-Bandwidth Memory (HBM) interface ontwerp is snel geëvolueerd om tegemoet te komen aan de toenemende eisen van AI-accelerators. Sinds de introductie van HBM heeft het verschillende generatiewijzigingen ondergaan, waarbij elke iteratie hogere doorvoer, grotere capaciteit en verbeterde energie-efficiëntie biedt. De oorspronkelijke HBM-standaard, ontwikkeld door Samsung Electronics Co., Ltd. en SK hynix Inc. in samenwerking met Advanced Micro Devices, Inc. (AMD), legde de basis voor het verticaal stapelen van DRAM-dies en het verbinden ervan met through-silicon vias (TSV’s), wat brede I/O en laag stroomverbruik mogelijk maakte.

HBM2 en HBM2E-standaarden, goedgekeurd door de JEDEC Solid State Technology Association, verhoogden verder de doorvoer en capaciteit per stack, met ondersteuning tot 3,6 Gbps per pin en 16 GB per stack. Deze verbeteringen waren cruciaal voor AI-accelerators, die snelle toegang tot grote datasets en modellen vereisen. De nieuwste HBM3-standaard, geïntroduceerd in 2022, verhoogt de doorvoer tot meer dan 6,4 Gbps per pin en stackcapaciteiten tot 24 GB, met Micron Technology, Inc. en SK hynix Inc. onder de eersten die HBM3-producten aankondigden. HBM3E, dat naar verwachting in 2025 op grote schaal zal worden aangenomen, levert naar verwachting nog hogere snelheden en verbeterd thermisch beheer, waarmee wordt ingespeeld op de behoeften van next-generation AI-werklasten.

Architectonisch gezien is de integratie van HBM met AI-accelerators verschoven van traditionele zij-aan-zij PCB-plaatsing naar 2.5D- en 3D-verpakkingen, zoals silicium interposers en geavanceerde chiplet-ontwerpen. NVIDIA Corporation en AMD hebben het gebruik van HBM in hun GPU’s en AI-accelerators gepionierd, door gebruik te maken van deze verpakkings technieken om signaalverlies te minimaliseren en de geheugendoorvoer te maximaliseren. De acceptatie van co-gepakte optica en on-die geheugencamera’s verschijnt ook, waardoor de latentie en het energieverbruik verder verminderen.

Kijkend naar 2025, wordt het HBM-interfaceontwerplandschap gekenmerkt door een focus op schaalbaarheid, energie-efficiëntie en geïntegreerde flexibiliteit. Industriële leiders werken samen aan nieuwe standaarden en referentiearchitecturen om de interoperabiliteit te waarborgen en de exponentiële groei in de omvang en complexiteit van AI-modellen te ondersteunen. Terwijl AI-accelerators blijven duwen op de grenzen van prestaties, blijft de evolutie van HBM-standaarden en architecturen een hoeksteen van innovatie in het veld.

Concurrentieanalyse: Voornaamste Spelers en Innovatietrends

Het competitieve landschap voor High-Bandwidth Memory (HBM) interface ontwerp in AI-accelerators evolueert snel, aangedreven door de toenemende eisen van kunstmatige intelligentie werklasten en de behoefte aan efficiënte, hoge-snelheid datatransfer tussen geheugen en verwerkings eenheden. Belangrijke spelers in de industrie, zoals Samsung Electronics Co., Ltd., Micron Technology, Inc., en SK hynix Inc. domineren de HBM-productie sector, elk met de introductie van opeenvolgende generaties van HBM (HBM2E, HBM3, en verder) met verhoogde doorvoer, capaciteit en energie-efficiëntie.

Aan de kant van AI-accelerators hebben bedrijven zoals NVIDIA Corporation en Advanced Micro Devices, Inc. (AMD) HBM geïntegreerd in hun vlaggenschip GPU’s en datacenter-accelerators, gebruikmakend van de brede interface van het geheugen en 3D-stapeling om knelpunten in deep learning en high-performance computing toepassingen te minimaliseren. Intel Corporation heeft ook HBM aangenomen in zijn AI- en HPC-producten, met een focus op het optimaliseren van de interface voor lagere latentie en hogere doorvoer.

Innovatietrends in HBM-interfaceontwerp zijn gericht op het maximaliseren van de doorvoer terwijl het energieverbruik en de fysieke voetafdruk worden verminderd. Technieken zoals geavanceerde through-silicon via (TSV) architecturen, verbeterde signaalintegriteit en dynamische spanning/frequentie scalen worden geïmplementeerd om deze uitdagingen aan te pakken. De acceptatie van HBM3 en de ontwikkeling van HBM4-standaarden, geleid door de JEDEC Solid State Technology Association, dringen de grenzen van geheugendoorvoer op, waarbij HBM3 zich richt op snelheden die meer dan 800 GB/s per stap overschrijden en HBM4 naar verwachting dit aanzienlijk zal overschrijden.

Een andere opmerkelijke trend is de co-verpakking van HBM met AI-accelerators met behulp van geavanceerde verpakkings technologieën zoals 2.5D en 3D integratie. Taiwan Semiconductor Manufacturing Company Limited (TSMC) en Amkor Technology, Inc. zijn toonaangevend in het aanbieden van deze verpakkingsoplossingen, die een nauwere integratie en verbeterd thermisch beheer mogelijk maken. Deze co-ontwerpprocedure is cruciaal voor next-generation AI-systemen, waarbij geheugendoorvoer en nabijheid van rekeneenheden direct invloed hebben op prestaties en efficiëntie.

Kortom, de competitieve dynamiek in HBM-interfaceontwerp voor AI-accelerators wordt gevormd door snelle innovatie, strategische partnerschappen tussen geheugen- en chipfabrikanten, en de ononderbroken zoektocht naar hogere doorvoer en oplossingen met een lager energieverbruik om te voldoen aan de behoeften van AI-gedreven werklasten.

Marktomvang en Vooruitzichten (2025–2030): CAGR, Omzetprojecties en Regionale Verdeling

De markt voor High-Bandwidth Memory (HBM) interface ontwerp in AI-accelerators staat op het punt robuuste groei te ervaren tussen 2025 en 2030, aangedreven door de toenemende vraag naar high-performance computing in kunstmatige intelligentie, machine learning en datacenter toepassingen. De wereldwijde HBM-interface markt wordt verwacht een samengestelde jaarlijkse groei (CAGR) van ongeveer 25–30% te registreren gedurende deze periode, wat de snelle adoptie van HBM-geconfigureerde AI-accelerators in zowel ondernemings- als cloud-omgevingen weerspiegelt.

Omzetprojecties geven aan dat de marktgrootte, gewaardeerd op een geschat $2,5 miljard in 2025, naar verwachting meer dan $7,5 miljard zou kunnen overschrijden tegen 2030. Deze toename is te danken aan de toenemende integratie van HBM in next-generation AI-chips, die ultra-snelle geheugensinterfaces vereisen om enorme parallelle verwerkingswerkzaamheden af te handelen. Belangrijke spelers in de industrie zoals Samsung Electronics Co., Ltd., Micron Technology, Inc., en SK hynix Inc. investeren aanzienlijk in R&D om HBM-interface technologieën verder te ontwikkelen, wat de marktuitbreiding verder aanwakkert.

Regionaal wordt verwacht dat Azië-Pacific de markt voor HBM-interfaceontwerp zal domineren, goed voor meer dan 45% van de wereldwijde omzet tegen 2030. Deze dominantie is gebaseerd op de aanwezigheid van belangrijke halfgeleiderfabrieken en geheugent fabrikanten in landen zoals Zuid-Korea, Taiwan en China. Noord-Amerika volgt nauw, gedreven door de concentratie van AI-acceleratorontwikkelaars en hyperscale datacenters in de Verenigde Staten en Canada. Europa ziet ook een gestage groei, met name in de sector van automotive AI en industriële automatisering.

De proliferatie van AI-gedreven toepassingen in edge computing, autonome voertuigen en high-frequency trading versnelt verder de adoptie van geavanceerde HBM-interfaces. Naarmate AI-modellen complexer en data-intensiever worden, dwingt de vraag naar hogere geheugendoorvoer en lagere latentie chipontwerpers om HBM2E, HBM3 en opkomende HBM4-standaarden te adopteren, zoals gedefinieerd door de JEDEC Solid State Technology Association.

Samenvattend, de HBM-interface ontwerpmakrt voor AI-accelerators staat op het punt om aanzienlijke uitbreiding te ondergaan tot 2030, met sterke regionale groei in Azië-Pacific en Noord-Amerika, en een duidelijke trend naar hogere doorvoer en energie-efficiënte geheugensystemen.

Aandrijvers en Uitdagingen: Prestatie-eisen, Energie-efficiëntie en Integratiecomplexiteit

De snelle evolutie van kunstmatige intelligentie (AI) werklasten heeft ongekende eisen gesteld aan geheugensystemen, waardoor High-Bandwidth Memory (HBM) een cruciale enabler is geworden voor next-generation AI-accelerators. Het ontwerp van HBM-interfaces moet rekening houden met verschillende belangrijke aandrijvers en uitdagingen, vooral op het gebied van prestaties, energie-efficiëntie en integratiecomplexiteit.

Prestatie-eisen: AI-accelerators vereisen enorme geheugendoorvoer om gegevens-hongerende computermotoren te voeden, vooral voor deep learning-modellen met miljarden parameters. HBM, met zijn 3D-gestapelde architectuur en brede I/O, biedt doorvoer die in de nieuwste generaties meer dan 1 TB/s overschrijdt. Het in de praktijk bereiken van deze cijfers vereist echter zorgvuldige interfaceontwerpen om de latentie te minimaliseren, de doorvoer te maximaliseren en de signaalintegriteit bij hoge datastromen te waarborgen. De interface moet ook efficiënte gegevensbewegingspatronen ondersteunen die typisch zijn voor AI-werklasten, zoals grote matrixvermenigvuldigingen en tensorbewerkingen, die extra druk uitoefenen op geheugencamera’s en interconnects.

Energie-efficiëntie: Naarmate AI-accelerators opschalen, wordt energieverbruik een kritieke beperking, zowel voor datacenterimplementaties als edge-toepassingen. De nabijheid van HBM tot de processor en het gebruik van through-silicon vias (TSV’s) verlagen de energie per bit in vergelijking met traditionele DDR-geheugen. Desondanks moet het interfaceontwerp de energie verder optimaliseren door geavanceerde signaaltechnieken, dynamische spanning- en frequentieschaling, en intelligente energiemanagementsystemen toe te passen. Het balanceren van hoge doorvoer met een laag energieverbruik blijft een voortdurende uitdaging, vooral nu geheugenkruizen in capaciteit en snelheid groeien. Organisaties zoals Samsung Electronics Co., Ltd. en Micron Technology, Inc. zijn actief bezig met het ontwikkelen van nieuwe HBM-generaties met verbeterde energie-efficiëntie.

Integratiecomplexiteiten: De integratie van HBM met AI-accelerators brengt aanzienlijke verpakkings- en systeemniveau-uitdagingen met zich mee. Het fysiek stapelen van geheugendies en de verbinding met de processor via silicium interposers of geavanceerde substraten vereisen nauwgezette fabricage en thermisch beheer. Signaalintegriteit, elektromagnetische interferentie en mechanische spanning moeten allemaal worden aangepakt om een betrouwbare werking te waarborgen. Bovendien moet de interface compatibel zijn met evoluerende normen, zoals die gedefinieerd door de JEDEC Solid State Technology Association, om interoperabiliteit en toekomstige schaalbaarheid te waarborgen. De complexiteit neemt toe naarmate accelerators chiplet-gebaseerde architecturen adopteren, wat robuuste HBM-interfaceoplossingen vereiste die heterogene integratie ondersteunen.

Samenvattend, het ontwerp van HBM-interfaces voor AI-accelerators in 2025 is gevormd door de noodzaak om extreme doorvoer te leveren, energie-efficiëntie te behouden en de complexiteiten van geavanceerde integraties te beheren, terwijl men gelijke tred houdt met de snelle innovaties in AI-hardware.

Opkomende Toepassingen: AI, HPC, Datacenters en Edge Computing

De snelle evolutie van kunstmatige intelligentie (AI), high-performance computing (HPC), datacenters en edge computing genereert een ongekende vraag naar geheugendoorvoer en -efficiëntie. High-Bandwidth Memory (HBM) interface ontwerp is een hoeksteen technologie voor AI-accelerators geworden, die de enorme parallelisme en datadoorvoer mogelijk maakt die vereist wordt door moderne deep learning en analytics werklasten. HBM bereikt dit door meerdere DRAM-dies verticaal te stapelen en ze te verbinden met through-silicon vias (TSV’s), wat resulteert in aanzienlijk hogere doorvoer en lager energieverbruik vergeleken met traditionele geheugen interfaces.

In AI-accelerators, zoals die ontwikkeld door NVIDIA Corporation en Advanced Micro Devices, Inc. (AMD), zijn HBM-interfaces cruciaal voor het voeden van gegevens naar duizenden verwerkingskernen zonder knelpunten. De laatste HBM3- en HBM3E-standaarden, zoals gedefinieerd door de JEDEC Solid State Technology Association, ondersteunen doorvoer die meer dan 1 TB/s per stap overschrijdt, wat essentieel is voor het trainen van grootschalige neurale netwerken en real-time inferentie in datacenters. Deze interfaces zijn nauw geïntegreerd met de accelerator-die met behulp van geavanceerde verpakkings technieken zoals 2.5D en 3D integratie, wat signaalverlies en latentie minimaliseert.

In HPC-omgevingen worden HBM’s hoge doorvoer en energie-efficiëntie benut om wetenschappelijke simulaties, financiële modellering en andere data-intensieve taken te versnellen. Supercomputers zoals die gebouwd door Cray Inc. en Fujitsu Limited maken gebruik van HBM-geconfigureerde processors om prestaties op petascale en exascale te behalen. Het interfaceontwerp moet uitdagingen zoals signaalintegriteit, thermisch beheer en foutcorrectie aanpakken om betrouwbare werking onder extreme werklasten te waarborgen.

Edge computing-apparaten, die compacte formaten en laag energieverbruik vereisen, beginnen ook HBM-interfaces te adopteren. Bedrijven zoals Samsung Electronics Co., Ltd. en SK hynix Inc. ontwikkelen HBM-oplossingen die zijn afgestemd op edge-AI-chips, waarbij de behoeften aan doorvoer in evenwicht worden gebracht met strikte energie- en thermische beperkingen.

Kijkend naar 2025, zal de voortdurende verfijning van HBM-interface ontwerpen cruciaal zijn voor het ondersteunen van de volgende generatie AI-, HPC- en edge-toepassingen. Innovaties in verpakkingen, signalering en architecturen van geheugencamera’s zullen de schaalbaarheid en efficiëntie van AI-accelerators verder verbeteren, zodat de geheugendoorvoer gelijke tred houdt met de exponentiële groei in computationele vraag.

Analyse van de Leveringsketen en Ecosysteem

De leveringsketen en het ecosysteem voor High-Bandwidth Memory (HBM) interface ontwerp in AI-accelerators wordt gekenmerkt door een complex netwerk van halfgeleiderfabrikanten, geheugensleveranciers, fabrieken en leveranciers van ontwerptools. HBM, met zijn verticaal gestapelde DRAM-dies en brede interface, is een cruciale enabler voor AI-accelerators, die de doorvoer en energie-efficiëntie bieden die nodig is voor grootschalige machine learning-werklasten. Het ontwerp en de integratie van HBM-interfaces vereisen nauwe samenwerking tussen geheugensleveranciers zoals Samsung Electronics Co., Ltd., Micron Technology, Inc., en SK hynix Inc., en vooraanstaande AI-chipontwerpers zoals NVIDIA Corporation en Advanced Micro Devices, Inc. (AMD).

Het ecosysteem wordt verder ondersteund door geavanceerde verpakkings- en interconnecttechnologieën, zoals silicium interposers en 2.5D/3D-integratie, aangeboden door fabrieken zoals Taiwan Semiconductor Manufacturing Company Limited (TSMC) en Intel Corporation. Deze fabrieken mogelijk maken de fysieke integratie van HBM-stacks met logische dies, waarbij signaalintegriteit en thermisch beheer bij hoge datastromen worden gewaarborgd. EDA-toolproviders, waaronder Synopsys, Inc. en Cadence Design Systems, Inc., bieden gespecialiseerde IP- en verificatieoplossingen om te voldoen aan de strenge timing-, stroom- en betrouwbaarheidseisen van HBM-interfaces.

Standaardisatie-inspanningen, geleid door organisaties zoals de JEDEC Solid State Technology Association, spelen een cruciale rol bij het definiëren van HBM-interface specificaties en het waarborgen van interoperabiliteit in de hele leveringsketen. De snelle evolutie van HBM-standaarden (bijvoorbeeld HBM3, HBM3E) vereist dat deelnemers aan het ecosysteem hun ontwerpprocessen en productieprocessen continu bijwerken. Bovendien versnelt de groeiende vraag naar AI-accelerators in datacenters en edge-apparaten de investeringen in capaciteitsuitbreiding en veerkracht van de leveringsketen, zoals blijkt uit recente aankondigingen van grote geheugenen fabriekspartners.

Samenvattend, het HBM-interfaceontwerp ecosysteem voor AI-accelerators in 2025 wordt gekenmerkt door diepe onderlinge afhankelijkheden tussen geheugensleveranciers, chipontwerpers, fabrieken, EDA-leveranciers en normgevende instanties. Deze samenwerkingsomgeving is essentieel voor het leveren van de hoogpresterende, energie-efficiënte geheugensystemen die de next-generation AI-werklasten onderbouwen.

Toekomstige Vooruitzichten: Ontwrichtende Technologieën en Volgende Generatie HBM Interfaces

De toekomst van High-Bandwidth Memory (HBM) interface ontwerp voor AI-accelerators staat op het punt om aanzienlijke transformatie te ondergaan, gedreven door ontwrichtende technologieën en de evolutie van next-generation HBM-standaarden. Terwijl AI-werklasten blijven vragen om hogere geheugendoorvoer en lagere latentie, beweegt de industrie zich voorbij HBM2E en HBM3 richting nog geavanceerdere oplossingen zoals HBM3E en vroeg onderzoek naar HBM4. Deze nieuwe standaarden beloven ongekende datasnelheden te leveren, met HBM3E die richt op snelheden tot 9,2 Gbps per pin en totale doorvoeren van meer dan 1,2 TB/s per stap, een cruciale sprong voor AI-training en inferentie op schaal (Samsung Electronics).

Ontwrichtende interface-technologieën ontstaan ook om de uitdagingen van signaalintegriteit, energievoorziening en thermisch beheer aan te pakken die inherent zijn aan het stapelen van meer geheugendies en de toename van I/O-dichtheid. Innovaties zoals geavanceerde through-silicon via (TSV) architecturen, verbeterde interposer-materialen en de acceptatie van chiplet-gebaseerde ontwerpen stellen nauwere integratie tussen AI-accelerators en HBM-stacks mogelijk. Bijvoorbeeld, het gebruik van siliciumbruggen en organische interposers wordt onderzocht om kosten te verlagen en de schaalbaarheid te verbeteren, terwijl de hoge snelheidssignaaloverdracht die vereist is door next-gen HBM wordt behouden (Advanced Micro Devices, Inc.).

Kijkend naar de toekomst, zal de integratie van HBM met opkomende AI-acceleratorarchitecturen – zoals die gebruik maken van 2.5D en 3D verpakkingen – de grenzen tussen geheugen en verwerking verder vervagen. Deze co-verpakkingsbenadering wordt verwacht om databeweging te minimaliseren, energieverbruik te verminderen en nieuwe niveaus van parallelisme te ontsluiten voor grote taalmodellen en generatieve AI-werk lasten. Industriële leiders werken ook samen aan nieuwe interfaceprotocollen en foutcorrectieschema’s om betrouwbaarheid en schaalbaarheid te waarborgen terwijl de geheugendoorvoer zich ontwikkelt (Micron Technology, Inc.).

Samenvattend, de toekomst van HBM-interfaceontwerp voor AI-accelerators zal worden gevormd door snelle ontwikkelingen in geheugentechnologie, verpakkingsinnovatie en systeemniveau co-ontwerp. Deze ontwikkelingen zijn ingesteld om het prestatiestandaard voor AI-hardware in 2025 en verder opnieuw te definiëren, en zullen de volgende golf van doorbraken in machine learning en data-analyse mogelijk maken.

Strategische Aanbevelingen voor Belanghebbenden

Naarmate AI-accelerators steeds meer afhankelijk zijn van high-bandwidth memory (HBM) om te voldoen aan de vraag naar grootschalige machine learning en deep learning werklasten, moeten belanghebbenden – waaronder chipontwerpers, systeemintegratoren en datacenteroperators – toekomstgerichte strategieën aannemen om HBM-interfaceontwerp te optimaliseren. De volgende aanbevelingen zijn op maat gemaakt om in te spelen op het evoluerende landschap van HBM-integratie in AI-hardware voor 2025 en verder.

- Prioritize Co-Design of Memory and Compute: Samenwerking tussen geheugen- en verwerkings teams is essentieel. Door de HBM-interface samen te optimaliseren met de architectuur van de AI-accelerator, kunnen belanghebbenden de latentie minimaliseren en de doorvoer maximaliseren. Bedrijven zoals Samsung Electronics Co., Ltd. en Micron Technology, Inc. hebben de voordelen van dergelijke geïntegreerde benaderingen in hun laatste HBM-oplossingen aangetoond.

- Adopt Latest HBM Standards: Actueel blijven met de laatste HBM-standaarden, zoals HBM3 en de opkomende HBM4, zorgt voor compatibiliteit en toegang tot hogere doorvoeren en verbeterde energie-efficiëntie. De JEDEC Solid State Technology Association actualiseert deze standaarden regelmatig, en vroege adoptie kan een concurrentievoordeel bieden.

- Invest in Advanced Packaging Technologies: 2.5D en 3D-integratie, zoals silicium interposers en through-silicon vias (TSV’s), zijn cruciaal voor efficiënt HBM-interfaceontwerp. Samenwerken met verpakkingsspecialisten zoals Taiwan Semiconductor Manufacturing Company Limited (TSMC) kan belanghebbenden helpen gebruik te maken van geavanceerde interconnectoplossingen.

- Optimize Power Delivery and Thermal Management: Naarmate HBM-stacks in dichtheid en snelheid groeien, worden energievoorziening en warmteafvoer uitdagender. Belanghebbenden moeten investeren in geavanceerde energiemanagement IC’s en innovatieve koeloplossingen, waarbij ze samenwerken met partners zoals CoolIT Systems Inc. voor thermisch beheer.

- Foster Ecosystem Collaboration: Betrokken raken bij industrieconsortia en normgevende instanties, zoals OIF (Optical Internetworking Forum), kan belanghebbenden helpen geïnformeerd te blijven over interface-innovaties en eisen voor interoperabiliteit.

Door deze strategische aanbevelingen toe te passen, kunnen belanghebbenden ervoor zorgen dat hun HBM-interfaceontwerpen voor AI-accelerators robuust, schaalbaar en toekomstbestendig blijven, ter ondersteuning van de volgende generatie AI-werklasten.

Bronnen & Referenties

- Micron Technology, Inc.

- NVIDIA Corporation

- JEDEC Solid State Technology Association

- Amkor Technology, Inc.

- Cray Inc.

- Fujitsu Limited

- Synopsys, Inc.

- OIF (Optical Internetworking Forum)