Dezvoltarea puterii memoriei cu lățime mare de bandă: Cum designul HBM redefinește acceleratorii AI în 2025 și dincolo de aceasta. Explorați tehnologiile, creșterea pieței și oportunitățile strategice care modelează următoarea eră a hardware-ului AI.

- Rezumat Executiv: Constatări Cheie și Informații Strategice

- Prezentare Generală a Pieței: Designul HBM pentru Acceleratorii AI în 2025

- Peisaj Tehnologic: Evoluția Standardelor și Arhitecturilor HBM

- Analiza Competitivă: Jucători Importanți și Tendințe în Inovație

- Dimensiunea Pieței și Prognoza (2025–2030): CAGR, Proiecții ale Veniturilor și Descompunerea Regională

- Factori și Provocări: Cerințe de Performanță, Eficiența Energetică și Complexități de Integrare

- Aplicații Emergente: AI, HPC, Centre de Date și Calcul Edge

- Analiza Lanțului de Aprovizionare și a Ecosistemului

- Perspectivele Viitoare: Tehnologii Disruptive și Interfețe HBM de Generație Viitoare

- Recomandări Strategice pentru Părțile Interesate

- Surse și Referințe

Rezumat Executiv: Constatări Cheie și Informații Strategice

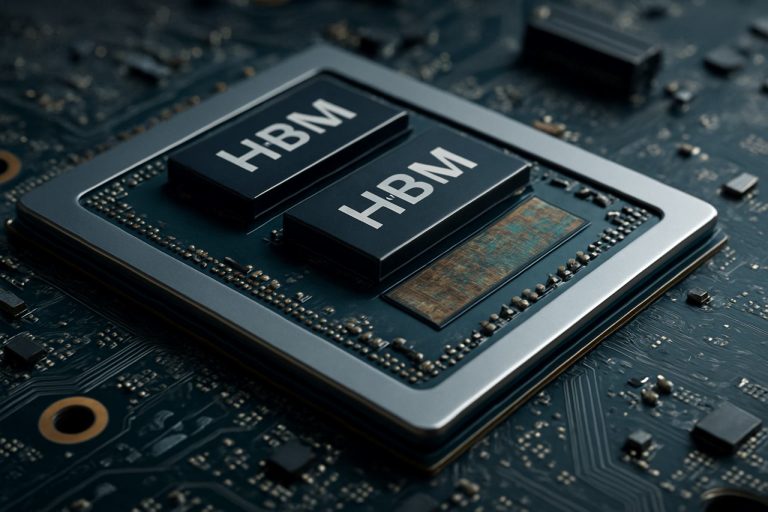

Designul interfeței memoriei cu lățime mare de bandă (HBM) a apărut ca un facilitator critic pentru acceleratorii AI de generație următoare, adresându-se cerințelor tot mai mari pentru lățimea de bandă a memoriei, eficiența energetică și forme compacte în aplicațiile intensive de date. În 2025, evoluția rapidă a sarcinilor de lucru AI—în special în învățarea profundă și modelele mari de limbaj—a intensificat nevoia de soluții de memorie care pot livra terabiți pe secundă de lățime de bandă, minimizând în același timp latența și consumul de energie. HBM, cu arhitectura sa 3D-stivuită și tehnologia vijelui prin siliciu (TSV), a devenit interfața de memorie preferată pentru principalii furnizori de acceleratorii AI.

Constatările cheie indică faptul că adoptarea HBM3 și desfășurarea anticipată a HBM4 stabilesc noi standarde în lățimea de bandă, HBM3 oferind până la 819 GB/s pe stivă, iar HBM4 așteptându-se să depășească 1 TB/s. Aceste avansuri permit acceleratorilor AI să proceseze seturi de date mai mari în timp real, îmbunătățind semnificativ prințul de antrenare și inferență. Marii jucători din industrie, cum ar fi Samsung Electronics Co., Ltd., Micron Technology, Inc. și SK hynix Inc. sunt în fruntea inovației HBM, colaborând strâns cu designerii de hardware AI pentru a optimiza protocoalele interfeței și integritatea semnalului.

Informațiile strategice relevă că designul de interfață HBM de succes se bazează pe mai mulți factori: tehnici avansate de ambalare (cum ar fi integrarea 2.5D și 3D), gestionarea termică robustă și co-designul controlerelor de memorie cu nuclee de procesare AI. Companii precum Advanced Micro Devices, Inc. și NVIDIA Corporation utilizează aceste strategii pentru a livra acceleratorii AI cu metrici de performanță pe watt fără precedent. În plus, integrarea HBM cu arhitecturi bazate pe chiplet câștigă teren, oferind modularitate și scalabilitate pentru sistemele AI viitoare.

Privind în viitor, ecosistemul interfeței HBM este așteptat să beneficieze de eforturile de standardizare conduse de organizații precum Asociația Tehnologiei Solid State JEDEC, care facilitează interoperabilitatea și accelerează timpul de lansare pe piață pentru noi soluții de memorie. Pe măsură ce modelele AI continuă să devină mai complexe, alinierea strategică a designului interfeței HBM cu sarcinile de lucru AI în evoluție va fi esențială pentru menținerea avantajului competitiv în peisajul hardware-ului AI.

Prezentare Generală a Pieței: Designul HBM pentru Acceleratorii AI în 2025

Piața pentru designul interfeței memoriei cu lățime mare de bandă (HBM) în acceleratorii AI este pregătită pentru o creștere semnificativă în 2025, condusă de cerințele computaționale tot mai mari ale sarcinilor de muncă de inteligență artificială și învățare automată. HBM, o tehnologie DRAM stivuită 3D, oferă îmbunătățiri substanțiale în lățimea de bandă a memoriei și eficiența energetică comparativ cu soluțiile de memorie tradiționale, făcând-o un facilitator critic pentru acceleratorii AI de generație următoare.

În 2025, adoptarea interfețelor HBM este accelerată de companii semiconductoare de frunte și operatori de centre de date hyperechipe care caută să depășească bottleneck-urile de memorie inerente în sarcinile de instruire și inferență AI. Cele mai recente standarde HBM, cum ar fi HBM3 și emergentul HBM3E, oferă lățimi de bandă care depășesc 1 TB/s pe dispozitiv, susținând cerințele de procesare paralelă ale modelor mari de limbaj și sistemelor de AI generativă. Companii cum ar fi Samsung Electronics Co., Ltd., Micron Technology, Inc. și SK hynix Inc. sunt în fruntea dezvoltării HBM, furnizând soluții de memorie care sunt rapid integrate în designurile acceleratorilor AI.

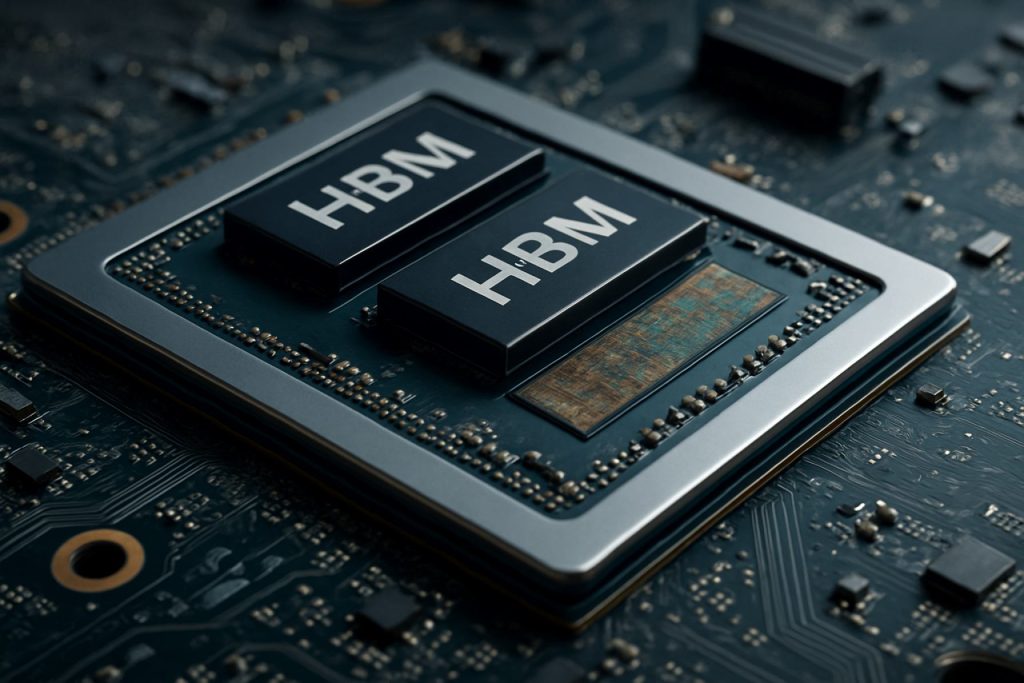

Designul interfeței pentru HBM în acceleratorii AI devine din ce în ce mai complex, necesitând tehnologii avansate de ambalare, cum ar fi integrarea 2.5D și 3D. Aceste metode permit apropierea fizică strânsă a stivelor HBM de unitățile de procesare, minizând latența și maximizând debitul de date. Fabricile de semiconductoare precum Taiwan Semiconductor Manufacturing Company Limited (TSMC) și Intel Corporation investesc în soluții avansate de interpozitare și ambalare pentru a susține aceste arhitecturi.

Cererea pentru acceleratorii AI cu HBM este deosebit de puternică în centrele de date cloud, computarea edge și sectorul calculului de înaltă performanță (HPC). Principalele companii de cipuri AI, inclusiv NVIDIA Corporation și Advanced Micro Devices, Inc. (AMD), integrează HBM în produsele lor de vârf pentru a livra lățimea de bandă a memoriei necesară pentru modelele AI de ultimă generație. Peisajul competitiv este, de asemenea, modelat de standardele în evoluție de la organizații precum Asociația Tehnologiei Solid State JEDEC, care continuă să definească noi specificații HBM pentru a satisface cerințele AI viitoare.

În general, piața designului interfeței HBM pentru acceleratorii AI în 2025 este caracterizată prin inovație rapidă, parteneriate strategice în întreaga lanț de aprovizionare semiconductor și o concentrare neîncetată pe lățimea de bandă, eficiența energetică și scalabilitate pentru a susține următoarea fază a avansurilor AI.

Peisaj Tehnologic: Evoluția Standardelor și Arhitecturilor HBM

Peisajul tehnologic pentru designul interfeței memoriei cu lățime mare de bandă (HBM) a evoluat rapid pentru a răspunde cerințelor tot mai mari ale acceleratorilor AI. De la introducerea sa, HBM a suferit mai multe îmbunătățiri generative, fiecare iterație livrând lățimi de bandă mai mari, capacitate crescută și eficiență energetică îmbunătățită. Primul standard HBM, dezvoltat de Samsung Electronics Co., Ltd. și SK hynix Inc. în colaborare cu Advanced Micro Devices, Inc. (AMD), a pregătit terenul pentru stivuirea die-urilor DRAM vertical și conectarea acestora cu vijeliile prin siliciu (TSV), permițând I/O-uri largi și consum de energie redus.

Standardele HBM2 și HBM2E, ratificate de Asociația Tehnologiei Solid State JEDEC, au crescut în continuare lățimea de bandă și capacitatea pe stivă, susținând până la 3.6 Gbps pe pin și 16 GB pe stivă. Aceste îmbunătățiri au fost critice pentru acceleratorii AI, care necesită acces rapid la seturi mari de date și modele. Cel mai recent standard HBM3, introdus în 2022, duce lățimea de bandă la peste 6.4 Gbps pe pin și capacități de stivă de până la 24 GB, cu Micron Technology, Inc. și SK hynix Inc. printre primii care au anunțat produse HBM3. HBM3E, care se așteaptă să fie adoptat pe scară largă în 2025, este proiectat să ofere chiar și viteze mai mari și o gestionare termică îmbunătățită, răspunzând nevoilor sarcinilor de lucru AI de generație următoare.

Arhitectural, integrarea HBM cu acceleratorii AI s-a mutat de la amplasarea tradițională pe PCB-uri, la ambalare 2.5D și 3D, cum ar fi interpozitoarele de siliciu și designurile avansate de chiplet. NVIDIA Corporation și AMD au fost pionierii utilizării HBM în GPU-urile și acceleratorii lor AI, profitând de aceste tehnici de ambalare pentru a minimiza pierderile de semnal și a maximiza lățimea de bandă a memoriei. Adoptarea opticii co-ambalate și a controlerelor de memorie on-die este, de asemenea, în creștere, reducând și mai departe latența și consumul de energie.

Privind spre 2025, peisajul designului interfeței HBM este caracterizat printr-o concentrare pe scalabilitate, eficiență energetică și flexibilitate de integrare. Liderii industriei colaborează la noi standarde și arhitecturi de referință pentru a asigura interoperabilitatea și pentru a susține creșterea exponențială a dimensiunii și complexității modelelor AI. Pe măsură ce acceleratorii AI continuă să împingă limitele performanței, evoluția standardelor și arhitecturilor HBM rămâne o piatră de temelie a inovației în domeniul.

Analiza Competitivă: Jucători Importanți și Tendințe în Inovație

Peisajul competitiv pentru designul interfeței memoriei cu lățime mare de bandă (HBM) în acceleratorii AI evoluează rapid, condus de cerințele tot mai mari ale sarcinilor de lucru de inteligență artificială și de necesitatea unui transfer de date eficient și de mare viteză între memorie și unitățile de procesare. Principalele companii din industrie, cum ar fi Samsung Electronics Co., Ltd., Micron Technology, Inc. și SK hynix Inc., domină sectorul de fabricare a HBM, fiecare introducând generații succesive de HBM (HBM2E, HBM3 și altele) cu lățimi de bandă, capacitate și eficiență energetică crescute.

Pe frontul acceleratorilor AI, companii precum NVIDIA Corporation și Advanced Micro Devices, Inc. (AMD) au integrat HBM în GPU-urile lor de vârf și în acceleratorii pentru centre de date, folosind interfața largă a memoriei și stivuirea 3D pentru a minimiza bottleneck-urile în aplicațiile de învățare profundă și calcul de înaltă performanță. Intel Corporation a adoptat, de asemenea, HBM în produsele sale AI și HPC, concentrându-se pe optimizarea interfeței pentru latență mai mică și debit mai mare.

Tendințele în inovația designului interfeței HBM se concentrează pe maximizarea lățimii de bandă, reducând în același timp consumul de energie și amprenta fizică. Tehnici precum arhitecturile avansate de vijelii prin siliciu (TSV), îmbunătățirea integrității semnalului și scalarea dinamică a tensiunii/unei frecvențe sunt implementate pentru a aborda aceste provocări. Adoptarea HBM3 și dezvoltarea standardelor HBM4, conduse de Asociația Tehnologiei Solid State JEDEC, împing limitele lățimii de bandă a memoriei, HBM3 având ca obiectiv viteze de peste 800 GB/s pe stivă, iar HBM4 fiind așteptat să depășească semnificativ acest lucru.

O altă tendință notabilă este co-ambalarea HBM cu acceleratorii AI folosind tehnologii avansate de ambalare, cum ar fi integrarea 2.5D și 3D. Taiwan Semiconductor Manufacturing Company Limited (TSMC) și Amkor Technology, Inc. sunt în fruntea furnizării acestor soluții de ambalare, permițând o integrare mai strânsă și o gestionare termică îmbunătățită. Această abordare de co-design este critică pentru sistemele AI de generație următoare, unde lățimea de bandă a memoriei și apropierea de unitățile de calcul influențează direct performanța și eficiența.

În rezumat, dinamica competitivă în designul interfeței HBM pentru acceleratorii AI este modelată de inovații rapide, parteneriate strategice între furnizorii de memorie și cipuri și căutarea neîncetată a soluțiilor de lățime de bandă mai mare și de putere mai mică pentru a satisface cerințele sarcinilor de lucru conduse de AI.

Dimensiunea Pieței și Prognoza (2025–2030): CAGR, Proiecții ale Veniturilor și Descompunerea Regională

Piața pentru designul interfeței memoriei cu lățime mare de bandă (HBM) în acceleratorii AI este pregătită pentru o creștere robustă între 2025 și 2030, stimulată de cererea în creștere pentru computație de înaltă performanță în inteligența artificială, învățarea automată și aplicațiile din centrele de date. Piața globală HBM pentru interfață este proiectată să înregistreze o rată de creștere anuală compusă (CAGR) de aproximativ 25–30% în această perioadă, reflectând adoptarea rapidă a acceleratorilor AI cu HBM în mediile de afaceri și cloud.

Proiecțiile veniturilor indică faptul că dimensiunea pieței, evaluată la aproximativ 2.5 miliarde de dolari în 2025, ar putea depăși 7.5 miliarde de dolari până în 2030. Această creștere se datorează integrării crescânde a HBM în cipurile AI de generație următoare, care necesită interfețe de memorie ultra-rapide pentru a gestiona sarcini de lucru masive de procesare paralelă. Principalele companii din industrie, cum ar fi Samsung Electronics Co., Ltd., Micron Technology, Inc. și SK hynix Inc. investesc masiv în R&D pentru a avansa tehnologiile interfeței HBM, alimentând astfel expansiunea pieței.

Din punct de vedere regional, Asia-Pacific se așteaptă să domine piața designului interfeței HBM, reprezentând peste 45% din veniturile globale până în 2030. Această dominație este susținută de prezența fabricilor de semiconductoare majore și a producătorilor de memorie din țări precum Coreea de Sud, Taiwan și China. America de Nord urmează îndeaproape, stimulată de concentrarea dezvoltatorilor de acceleratorii AI și a centrelor de date hipo-scalate în Statele Unite și Canada. Europa observă, de asemenea, o creștere constantă, în special în sectoarele AI auto și automatizarea industrială.

Proliferarea aplicațiilor conduse de AI în computarea edge, vehicule autonome și comerțul de înaltă frecvență accelerează și mai mult adoptarea interfețelor avansate HBM. Pe măsură ce modelele AI devin mai complexe și mai intensive în date, nevoia de lățimi de bandă mai mari pentru memorie și latență mai mică împinge designerii de cipuri să adopte standardele HBM2E, HBM3 și emergente HBM4, așa cum sunt definite de Asociația Tehnologiei Solid State JEDEC.

În rezumat, piața designului interfeței HBM pentru acceleratorii AI este setată pentru o expansiune semnificativă până în 2030, cu o creștere regională puternică în Asia-Pacific și America de Nord și o tendință clară către soluții de memorie cu lățime de bandă mai mare și mai eficiente energetic.

Factori și Provocări: Cerințe de Performanță, Eficiența Energetică și Complexități de Integrare

Evoluția rapidă a sarcinilor de lucru de inteligență artificială (AI) a impus cerințe fără precedent asupra subsistemelor de memorie, făcând din memoria cu lățime mare de bandă (HBM) un facilitator critic pentru acceleratorii AI de generație următoare. Designul interfețelor HBM trebuie să abordeze mai mulți factori și provocări cheie, în special în domeniile performanței, eficienței energetice și complexității integrării.

Cerințe de Performanță: Acceleratorii AI necesită lățimi de bandă masive pentru a alimenta motoarele de calcul care consumă multe date, în special pentru modelele de învățare profundă cu miliarde de parametri. HBM, cu arhitectura sa 3D-stivuită și I/O-urile largi, oferă lățimi de bandă care depășesc 1 TB/s în cele mai recente generații. Totuși, atingerea acestui lucru în practică necesită un design atent al interfeței pentru a minimiza latența, a maximiza debitul și a asigura integritatea semnalului la rate mari de date. Interfața trebuie să susțină, de asemenea, modele eficiente de mișcare a datelor caracteristice sarcinilor de lucru AI, cum ar fi înmulțirile matricei mari și operațiile tensoriale, care pun o presiune suplimentară asupra controlerelor de memorie și interconectărilor.

Eficiența Energetică: Pe măsură ce acceleratorii AI se scalarează, consumul de energie devine o constrângere critică, atât pentru desfășurările din centrele de date, cât și pentru aplicațiile edge. Apropierea HBM de procesor și utilizarea vijeliilor prin siliciu (TSV) reduc energia pe bit comparativ cu memoria DDR tradițională. Cu toate acestea, designul interfeței trebuie să optimizeze și mai mult puterea prin utilizarea tehnicilor avansate de semnalizare, scalarea dinamică a tensiunii și frecvenței și managementul inteligent al energiei. Echilibrarea unei lățimi de bandă mari cu operarea la putere mică este o provocare persistentă, în special pe măsură ce stivele de memorie cresc în capacitate și viteză. Organizații precum Samsung Electronics Co., Ltd. și Micron Technology, Inc. dezvoltă activ noi generații de HBM cu eficiență energetică îmbunătățită.

Complexități de Integrare: Integrarea HBM cu acceleratorii AI implică provocări semnificative de ambalare și la nivel de sistem. Stivuirea fizică a die-urilor de memorie și conexiunea acestora la procesor prin interpozitoarele de siliciu sau substraturi avansate necesită fabricate precise și gestionarea termică. Integritatea semnalului, interferența electromagnetică și stresul mecanic trebuie să fie abordate pentru a asigura funcționarea fiabilă. În plus, interfața trebuie să fie compatibilă cu standardele în evoluție, cum ar fi cele definite de Asociația Tehnologiei Solid State JEDEC, pentru a asigura interoperabilitatea și scalabilitatea viitoare. Complexitatea crește pe măsură ce acceleratorii adoptă arhitecturi bazate pe chiplet, necesită soluții robuste de interfață HBM care să poată susține integrarea eterogenă.

În rezumat, designul interfețelor HBM pentru acceleratorii AI în 2025 este modelat de nevoia de a livra lățimi de bandă extreme, a menține eficiența energetică și a gestiona complexitățile integrării avansate, menținând în același timp ritmul cu inovația rapidă în hardware-ul AI.

Aplicații Emergente: AI, HPC, Centre de Date și Calcul Edge

Evoluția rapidă a inteligenței artificiale (AI), calculului de înaltă performanță (HPC), centrelor de date și computării edge generează o cerere fără precedent pentru lățimea de bandă și eficiența memoriei. Designul interfeței memoriei cu lățime mare de bandă (HBM) a devenit o tehnologie de bază pentru acceleratorii AI, permițând paralelismul masiv și debitul de date necesar de sarcinile de lucru moderne de învățare profundă și analitică. HBM realizează acest lucru prin stivuirea mai multor die-uri DRAM vertical și conectându-le cu vijelii prin siliciu (TSV), rezultând în lățimi de bandă semnificativ mai mari și un consum de energie mai redus comparativ cu interfețele de memorie tradiționale.

În acceleratorii AI, cum ar fi cei dezvoltați de NVIDIA Corporation și Advanced Micro Devices, Inc. (AMD), interfețele HBM sunt critice pentru alimentarea datelor către mii de nuclee de procesare fără bottleneck-uri. Cele mai recente standarde HBM3 și HBM3E, așa cum sunt definite de Asociația Tehnologiei Solid State JEDEC, susțin lățimi de bandă care depășesc 1 TB/s pe stivă, ceea ce este esențial pentru antrenarea rețelelor neuronale la scară mare și inferența în timp real în centrele de date. Aceste interfețe sunt integrate strâns cu die-ul acceleratorului folosind tehnici avansate de ambalare, cum ar fi integrarea 2.5D și 3D, minimizând pierderea semnalului și latența.

În medii HPC, lățimea de bandă ridicată și eficiența energetică a HBM sunt utilizate pentru a accelera simulările științifice, modelarea financiară și alte sarcini intensive în date. Supercomputerele, cum ar fi cele construite de Cray Inc. și Fujitsu Limited, utilizează procesoare habilitate HBM pentru a atinge obiective de performanță petascale și exascale. Designul interfeței trebuie să abordeze provocări precum integritatea semnalului, gestionarea termică și corecția erorilor pentru a asigura funcționarea fiabilă sub sarcini extreme.

Dispozitivele de calcul edge, care necesită forme compacte și un consum redus de energie, încep, de asemenea, să adopte interfețele HBM. Companii precum Samsung Electronics Co., Ltd. și SK hynix Inc. dezvoltă soluții HBM adaptate pentru cipurile AI edge, echilibrând nevoile de lățime de bandă cu constrângerile stricte de putere și termice.

Privind înainte spre 2025, continuarea perfecționării designului interfeței HBM va fi esențială pentru susținerea următoarei generații de aplicații AI, HPC și edge. Inovațiile în ambalare, semnalizare și arhitecturi de controlere de memorie vor îmbunătăți în continuare scalabilitatea și eficiența acceleratorilor AI, asigurându-se că lățimea de bandă a memoriei ține pasul cu cererea computațională exponențială.

Analiza Lanțului de Aprovizionare și a Ecosistemului

Lanțul de aprovizionare și ecosistemul pentru designul interfeței memoriei cu lățime mare de bandă (HBM) în acceleratorii AI este caracterizat de o rețea complexă de producători de semiconductoare, furnizori de memorie, fabrici și furnizori de instrumente de design. HBM, cu die-urile sale DRAM stivuite vertical și interfața largă, este un facilitator critic pentru acceleratorii AI, oferind lățimea de bandă și eficiența energetică necesare pentru sarcinile de învățare automată la scară largă. Designul și integrarea interfețelor HBM necesită o colaborare strânsă între furnizorii de memorie, cum ar fi Samsung Electronics Co., Ltd., Micron Technology, Inc. și SK hynix Inc. și principalii designeri de cipuri AI precum NVIDIA Corporation și Advanced Micro Devices, Inc. (AMD).

Ecosistemul este susținut și de tehnologii avansate de ambalare și interconectare, cum ar fi interpozitoarele de siliciu și integrarea 2.5D/3D, furnizate de fabrici precum Taiwan Semiconductor Manufacturing Company Limited (TSMC) și Intel Corporation. Aceste fabrici permit integrarea fizică a stivelor HBM cu die-urile logice, asigurând integritatea semnalului și gestionarea termică la rate mari de date. Furnizorii de instrumente EDA, inclusiv Synopsys, Inc. și Cadence Design Systems, Inc., oferă soluții specializate de IP și verificare pentru a aborda cerințele stricte de timp, putere și fiabilitate ale interfețelor HBM.

Eforturile de standardizare, conduse de organizații precum Asociația Tehnologiei Solid State JEDEC, joacă un rol esențial în definirea specificațiilor interfeței HBM și asigurarea interoperabilității în lanțul de aprovizionare. Evoluția rapidă a standardelor HBM (de exemplu, HBM3, HBM3E) necesită ca participanții la ecosistem să își actualizeze continuu fluxurile de design și procesele de fabricație. În plus, cererea în creștere pentru acceleratorii AI în centrele de date și în dispozitivele edge stimulează investițiile în extinderea capacității și reziliența lanțului de aprovizionare, așa cum se vede în anunțurile recente din partea principalelor parteneri de memorie și fabrici.

În rezumat, ecosistemul designului interfeței HBM pentru acceleratorii AI în 2025 este marcat de interdependențe profunde între furnizorii de memorie, designerii de cipuri, fabrici, furnizorii EDA și organismele de standardizare. Acest mediu colaborativ este esențial pentru livrarea subsistemelor de memorie de înaltă performanță și eficiente din punct de vedere energetic care stau la baza sarcinilor de lucru AI de generație următoare.

Perspectivele Viitoare: Tehnologii Disruptive și Interfețe HBM de Generație Viitoare

Viitorul designului interfeței memoriei cu lățime mare de bandă (HBM) pentru acceleratorii AI este pregătit pentru o transformare semnificativă, determinată de tehnologii disruptive și evoluția standardelor HBM de generație următoare. Pe măsură ce sarcinile de lucru AI continuă să ceară lățimi de bandă mai mari și latențe mai mici, industria se îndreaptă dincolo de HBM2E și HBM3 spre soluții și mai avansate, cum ar fi HBM3E și cercetări timpurii în HBM4. Aceste noi standarde promit să ofere rate de date fără precedent, cu HBM3E având ca obiectiv viteze de până la 9.2 Gbps pe pin și lățimi de bandă totale care depășesc 1.2 TB/s pe stivă, un salt critic pentru antrenarea și inferența AI la scară (Samsung Electronics).

Tehnologiile de interfață disruptive sunt, de asemenea, în curs de apariție pentru a aborda provocările integrității semnalului, livrării energiei și gestionării termice inerente stivuirea mai multor die-uri de memorie și creșterea densității I/O. Inovațiile precum arhitecturile avansate de vijelii prin siliciu (TSV), materiale de interpoză îmbunătățite și adoptarea designurilor bazate pe chiplet permit o integrare mai strânsă între acceleratorii AI și stivele HBM. De exemplu, utilizarea punților de siliciu și a interpozitelor organice este explorată pentru a reduce costul și a îmbunătăți scalabilitatea, menținând în același timp semnalizarea de mare viteză necesară de HBM de generație următoare (Advanced Micro Devices, Inc.).

Privind spre viitor, integrarea HBM cu arhitecturile emergente de accelerator AI—cum ar fi cele care profită de ambalarea 2.5D și 3D—va estompa și mai departe liniile dintre memorie și calcul. Această abordare de co-ambalare este așteptată să minimizeze mișcarea datelor, să reducă consumul de energie și să deblocheze noi niveluri de paralelism pentru modelele mari de limbaj și sarcinile de lucru AI generative. Liderii din industrie colaborează de asemenea la noi protocoale de interfață și scheme de corecție a erorilor pentru a asigura fiabilitatea și scalabilitatea pe măsură ce lățimile de bandă ale memoriei cresc (Micron Technology, Inc.).

În rezumat, viitorul designului interfeței HBM pentru acceleratorii AI va fi modelat de avansuri rapide în tehnologia memoriei, inovații în ambalare și co-design la nivel de sistem. Aceste dezvoltări sunt pregătite să redefinească performanța hardware-ului AI în 2025 și dincolo de aceasta, facilitând următoarea valvă de descoperiri în învățarea automată și analitica datelor.

Recomandări Strategice pentru Părțile Interesate

Pe măsură ce acceleratorii AI se bazează din ce în ce mai mult pe memorie cu lățime mare de bandă (HBM) pentru a satisface cerințele sarcinilor de muncă de învățare automată pe scară largă și învățare profundă, părțile interesate—inclusiv designerii de cipuri, integratorii de sisteme și operatorii de centre de date—trebuie să adopte strategii orientate spre viitor pentru a optimiza designul interfeței HBM. Următoarele recomandări sunt adaptate pentru a aborda peisajul în evoluție al integrării HBM în hardware-ul AI pentru 2025 și dincolo de aceasta.

- Prioritizează Co-Designul Memoriei și Calculului: Dezvoltarea colaborativă între echipele de memorie și calcul este esențială. Prin co-optimizarea interfeței HBM cu arhitectura acceleratorului AI, părțile interesate pot minimiza latența și maximiza debitul. Companii precum Samsung Electronics Co., Ltd. și Micron Technology, Inc. au demonstrat beneficiile acestor abordări integrate în cele mai recente soluții HBM.

- Adoptă Cele Mai Recente Standarde HBM: Menținerea actualității cu cele mai recente standarde HBM, cum ar fi HBM3 și emergentul HBM4, asigură compatibilitatea și accesul la lățimi de bandă mai mari și eficiență energetică îmbunătățită. Asociația Tehnologiei Solid State JEDEC actualizează regulat aceste standarde, iar adoptarea timpurie poate oferi un avantaj competitiv.

- Investește în Tehnologii Avansate de Ambalare: Integrarea 2.5D și 3D, cum ar fi interpozitoarele de siliciu și vijeliile prin siliciu (TSV), este esențială pentru un design eficient al interfeței HBM. Colaborarea cu specialiști în ambalare precum Taiwan Semiconductor Manufacturing Company Limited (TSMC) poate ajuta părțile interesate să profite de soluții de interconectare de vârf.

- Optimizează Livrarea Energiei și Gestionarea Termică: Pe măsură ce stivele HBM cresc în densitate și viteză, livrarea de energie și disiparea căldurii devin mai provocatoare. Părțile interesate ar trebui să investească în IC-uri avansate de management al energiei și soluții inovatoare de răcire, colaborând cu parteneri precum CoolIT Systems Inc. pentru gestionarea termică.

- Încurajează Colaborarea Ecosistemului: Implicarea în consorții industriale și organisme de standardizare, cum ar fi OIF (Optical Internetworking Forum), poate ajuta părțile interesate să rămână informate despre inovațiile în interfețe și cerințele de interoperabilitate.

Prin implementarea acestor recomandări strategice, părțile interesate pot asigura că designurile lor de interfață HBM pentru acceleratorii AI rămân robuste, scalabile și pregătite pentru viitor, susținând următoarea generație de sarcini de lucru AI.

Surse și Referințe

- Micron Technology, Inc.

- NVIDIA Corporation

- Asociația Tehnologiei Solid State JEDEC

- Amkor Technology, Inc.

- Cray Inc.

- Fujitsu Limited

- Synopsys, Inc.

- OIF (Optical Internetworking Forum)