Раскрытие потенциала памяти высокой полосы пропускания: Как проектирование интерфейса HBM революционизирует AI-ускорители в 2025 году и далее. Изучите технологии, рост рынка и стратегические возможности, определяющие следующую эпоху аппаратного обеспечения AI.

- Исполнительное резюме: ключевые выводы и стратегические инсайты

- Обзор рынка: проектирование интерфейса HBM для AI-ускорителей в 2025 году

- Технологический ландшафт: эволюция стандартов и архитектур HBM

- Конкурентный анализ: ведущие игроки и тенденции инноваций

- Размер рынка и прогноз (2025–2030): CAGR, прогноз доходов и региональный анализ

- Драйверы и проблемы: требования к производительности, эффективность потребления энергии и сложности интеграции

- Новые применения: AI, HPC, центры данных и периферийные вычисления

- Анализ цепочки поставок и экосистемы

- Будущий прогноз: разрушительные технологии и интерфейсы HBM нового поколения

- Стратегические рекомендации для заинтересованных сторон

- Источники и ссылки

Исполнительное резюме: ключевые выводы и стратегические инсайты

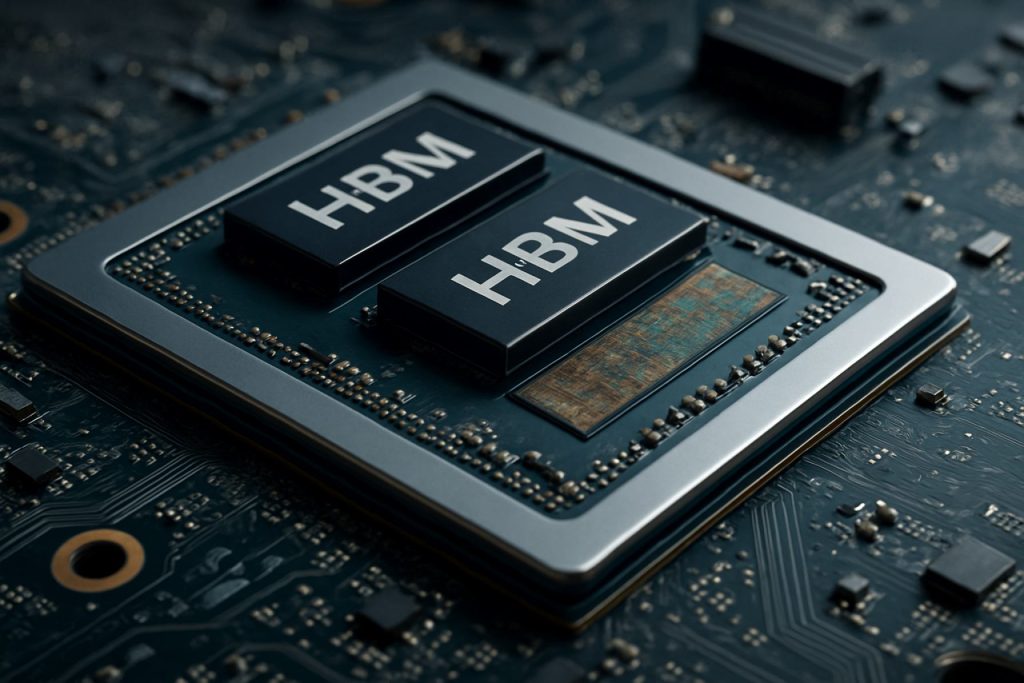

Дизайн интерфейса памяти высокой полосы пропускания (HBM) стал критически важным фактором для ускорителей AI следующего поколения, удовлетворяющим растущие требования к памяти, энергоэффективности и компактным форм-факторам в данных, требующих интенсивных приложениях. В 2025 году стремительное развитие загрузок AI — особенно в области глубокого обучения и крупных языковых моделей — усиливает необходимость в решениях для памяти, способных обеспечивать терабайты в секунду пропускной способности при минимизации задержек и потребления энергии. HBM с его 3D-структурой и технологией черезкремниевыеvias (TSV) стал предпочтительным интерфейсом памяти для ведущих поставщиков ускорителей AI.

Ключевые выводы показывают, что внедрение HBM3 и ожидаемое введение HBM4 устанавливают новые стандарты по пропускной способности, при этом HBM3 предлагает до 819 ГБ/с на стек, а HBM4 ожидается на уровне свыше 1 ТБ/с. Эти достижения позволяют AI-ускорителям обрабатывать более крупные наборы данных в реальном времени, значительно улучшая производительность обучения и вывода. Крупные игроки отрасли, такие как Samsung Electronics Co., Ltd., Micron Technology, Inc. и SK hynix Inc. находятся на переднем крае инноваций HBM, тесно сотрудничая с дизайнерами аппаратного обеспечения AI для оптимизации протоколов интерфейса и целостности сигнала.

Стратегические выводы показывают, что успешный дизайн интерфейса HBM зависит от нескольких факторов: передовых технологий упаковки (таких как 2.5D и 3D интеграция), надежного термического управления и совместного проектирования контроллеров памяти с вычислительными ядрами AI. Компании, такие как Advanced Micro Devices, Inc. и NVIDIA Corporation, используют эти стратегии для создания AI-ускорителей с беспрецедентными показателями производительности на ватт. Более того, интеграция HBM с архитектурами на базе чиплетов приобретает популярность, предлагая модульность и масштабируемость для будущих систем AI.

Смотрим вперед, экосистема интерфейсов HBM ожидает выгоды от усилий по стандартизации, инициированных организациями, такими как JEDEC Solid State Technology Association, которые упрощают совместимость и ускоряют выход на рынок новых решений для памяти. Поскольку модели AI продолжают расти в сложности, стратегическая интеграция дизайна интерфейса HBM с развивающимися рабочими нагрузками AI будет необходима для поддержания конкурентных преимуществ на рынке аппаратного обеспечения AI.

Обзор рынка: проектирование интерфейса HBM для AI-ускорителей в 2025 году

Рынок проектирования интерфейса памяти высокой полосы пропускания (HBM) в AI-ускорителях готов к значительному росту в 2025 году, что вызвано нарастающими вычислительными требованиями задач искусственного интеллекта и машинного обучения. HBM, технология 3D-стекового ДРАМ, предлагает существенные улучшения в области пропускной способности памяти и энергоэффективности по сравнению с традиционными решениями для памяти, что делает его критическим элементом для AI-ускорителей следующего поколения.

В 2025 году принятие интерфейсов HBM ускоряется ведущими полупроводниковыми компаниями и операторами гипермасштабных центров обработки данных, стремящимися преодолеть узкие места памяти, присущие задачам обучения и вывода AI. Последние стандарты HBM, такие как HBM3 и появляющийся HBM3E, предлагают пропускную способность более 1 ТБ/с на устройство, поддерживая требования параллельной обработки крупных языковых моделей и генеративных систем AI. Компании, такие как Samsung Electronics Co., Ltd., Micron Technology, Inc. и SK hynix Inc., находятся на переднем крае разработки HBM, поставляя решения для памяти, которые быстро интегрируются в дизайны AI-ускорителей.

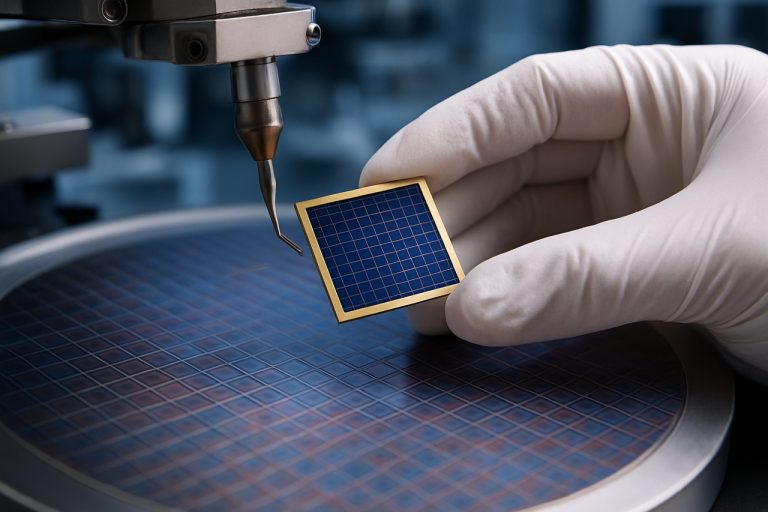

Дизайн интерфейса для HBM в AI-ускорителях становится все более сложным, требуя передовых технологий упаковки, таких как 2.5D и 3D интеграция. Эти подходы обеспечивают близкое физическое расположение стеков HBM к вычислительным единицам, минимизируя задержку и максимизируя пропускную способность данных. Полупроводниковые фабрики, такие как Taiwan Semiconductor Manufacturing Company Limited (TSMC) и Intel Corporation, инвестируют в передовые решения по интерposer и упаковке для поддержки этих архитектур.

Спрос на ускорители AI с поддержкой HBM особенно силен в облачных центрах данных, периферийных вычислениях и секторах высокопроизводительных вычислений (HPC). Крупные поставщики AI-чипов, включая NVIDIA Corporation и Advanced Micro Devices, Inc. (AMD), интегрируют HBM в свои флагманские продукты, чтобы обеспечить необходимую пропускную способность памяти для современных моделей AI. Конкурентный ландшафт также формируется развивающимися стандартами от организаций, таких как JEDEC Solid State Technology Association, которые продолжают определять новые спецификации HBM для удовлетворения будущих требований AI.

В целом, рынок проектирования интерфейсов HBM для AI-ускорителей в 2025 году характеризуется быстрыми инновациями, стратегическими партнерствами по всей цепочке поставок полупроводников и настойчивым вниманием к пропускной способности, энергоэффективности и масштабируемости в поддержке следующей волны достижений в области AI.

Технологический ландшафт: эволюция стандартов и архитектур HBM

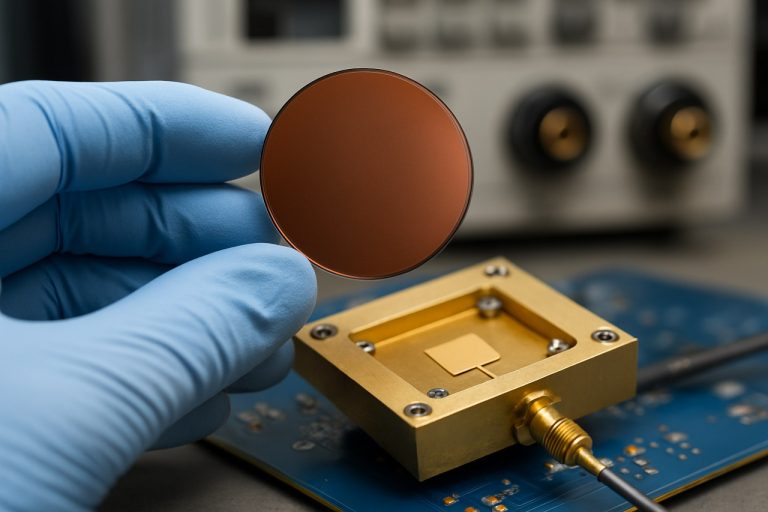

Технологический ландшафт проектирования интерфейсов памяти высокой полосы пропускания (HBM) быстро развивался, чтобы удовлетворить растущие требования AI-ускорителей. С момента своего внедрения HBM претерпел несколько поколений улучшений, каждая итерация обеспечивала более высокую пропускную способность, увеличенную емкость и повышенную энергоэффективность. Начальный стандарт HBM, разработанный Samsung Electronics Co., Ltd. и SK hynix Inc. в сотрудничестве с Advanced Micro Devices, Inc. (AMD), заложил основу для вертикальной упаковки чипов ДРАМ и их соединения через кремниевые vias (TSVs), что позволило достичь широкой I/O и низкого потребления энергии.

Стандарты HBM2 и HBM2E, ратифицированные JEDEC Solid State Technology Association, дополнительно увеличили пропускную способность и емкость на стек, поддерживая до 3.6 Гбит/с на вывод и 16 ГБ на стек. Эти улучшения были критически важны для AI-ускорителей, которым требуется быстрый доступ к большим наборам данных и моделям. Последний стандарт HBM3, представленный в 2022 году, увеличивает пропускную способность до более чем 6.4 Гбит/с на вывод и емкости стеков до 24 ГБ, при этом Micron Technology, Inc. и SK hynix Inc. стали первыми, кто объявил о продуктах HBM3. HBM3E, который ожидается для широкого внедрения в 2025 году, прогнозирует еще более высокие скорости и улучшенное термическое управление, удовлетворяя потребности рабочих нагрузок следующего поколения AI.

С архитектурной точки зрения интеграция HBM с AI-ускорителями изменилась от традиционной боковой установки на печатной плате к 2.5D и 3D упаковке, такой как кремниевые interposers и передовые конструкции чиплетов. NVIDIA Corporation и AMD стали пионерами использования HBM в своих GPU и AI-ускорителях, используя эти технологии упаковки для минимизации потерь сигнала и максимизации пропускной способности памяти. Адаптация совместно упакованных оптики и контроллеров памяти на кристалле также возникает, что дополнительно снижает задержки и потребление энергии.

Смотрим в будущее на 2025 год, ландшафт проектирования интерфейса HBM характеризуется акцентом на масштабируемости, энергоэффективности и гибкости интеграции. Лидеры отрасли сотрудничают по новым стандартам и эталонным архитектурам, чтобы обеспечить совместимость и поддерживать экспоненциальный рост размеров и сложности моделей AI. Поскольку AI-ускорители продолжают расширять границы производительности, эволюция стандартов и архитектур HBM остается краеугольным камнем инноваций в этой области.

Конкурентный анализ: ведущие игроки и тенденции инноваций

Конкурентная среда проектирования интерфейсов памяти высокой полосы пропускания (HBM) в AI-ускорителях быстро развивается, под воздействием растущих требований задач искусственного интеллекта и необходимости эффективной, высокоскоростной передачи данных между памятью и вычислительными единицами. Ведущие игроки отрасли, такие как Samsung Electronics Co., Ltd., Micron Technology, Inc. и SK hynix Inc. доминируют в секторе производства HBM, каждый вводя последовательные поколения HBM (HBM2E, HBM3 и далее) с увеличенной пропускной способностью, емкостью и энергоэффективностью.

На фронте AI-ускорителей компании, такие как NVIDIA Corporation и Advanced Micro Devices, Inc. (AMD), интегрировали HBM в свои флагманские GPU и ускорители центров обработки данных, используя широкое подключение памяти и 3D-стек для минимизации узких мест в глубоких обучающих и высокопроизводительных вычислительных приложениях. Intel Corporation также внедрила HBM в своих продуктах AI и HPC, сосредоточившись на оптимизации интерфейса для более низкой задержки и более высокой пропускной способности.

Тенденции инноваций в дизайне интерфейсов HBM сосредоточены на максимизации пропускной способности при одновременном снижении потребления энергии и физического размера. Для решения этих проблем внедряются такие методы, как передовые архитектуры черезкремниевых vias (TSV), улучшенная целостность сигнала и масштабирование динамического напряжения/частоты. Принятие HBM3 и разработка стандартов HBM4, инициированные JEDEC Solid State Technology Association, расширяют границы пропускной способности памяти, причем HBM3 нацеливается на скорости более 800 ГБ/с на стек, а HBM4, как ожидается, значительно превысит это.

Еще одной заметной тенденцией является совместная упаковка HBM с AI-ускорителями с использованием передовых технологий упаковки, таких как 2.5D и 3D интеграция. Taiwan Semiconductor Manufacturing Company Limited (TSMC) и Amkor Technology, Inc. занимают лидирующие позиции в предоставлении этих решений по упаковке, позволяя более тесную интеграцию и улучшенное термическое управление. Этот подход совместного проектирования имеет ключевое значение для систем AI следующего поколения, где пропускная способность памяти и близость к вычислительным единицам напрямую влияют на производительность и эффективность.

В заключение, конкурентная динамика в проектировании интерфейсов HBM для AI-ускорителей формируется быстрыми инновациями, стратегическими партнерствами между производителями памяти и чипов, и непрекращающимся стремлением к более высокой пропускной способности и низким потреблением энергии для удовлетворения потребностей задач, основанных на AI.

Размер рынка и прогноз (2025–2030): CAGR, прогноз доходов и региональный анализ

Рынок проектирования интерфейсов памяти высокой полосы пропускания (HBM) в AI-ускорителях готов к устойчивому росту между 2025 и 2030 годами, вызванному растущим спросом на высокопроизводительные вычисления в области искусственного интеллекта, машинного обучения и применении центров обработки данных. Ожидается, что глобальный рынок интерфейсов HBM зарегистрирует среднегодовой темп роста (CAGR) примерно 25–30% в этот период, отражая быстрое принятие AI-ускорителей с поддержкой HBM как в корпоративной, так и в облачной средах.

Прогнозы доходов указывают на то, что размер рынка, оцененный примерно в 2.5 миллиарда долларов в 2025 году, может превысить 7.5 миллиарда долларов к 2030 году. Этот рост связан с увеличением интеграции HBM в чипах AI следующего поколения, которые требуют ультрабыстрых интерфейсов памяти для обработки массивных параллельных рабочих нагрузок. Ключевые игроки отрасли, такие как Samsung Electronics Co., Ltd., Micron Technology, Inc. и SK hynix Inc., активно инвестируют в НИОКР для продвижения технологий интерфейсов HBM, что способствует дальнейшему расширению рынка.

Регионально, ожидается, что Азиатско-Тихоокеанский регион будет доминировать на рынке проектирования интерфейсов HBM, составляя более 45% глобального дохода к 2030 году. Это доминирование поддерживается присутствием крупных полупроводниковых фабрик и производителей памяти в таких странах, как Южная Корея, Тайвань и Китай. Северная Америка идет следом, что обусловлено сосредоточением разработчиков AI-ускорителей и гипермасштабных центров обработки данных в США и Канаде. Европа также демонстрирует устойчивый рост, особенно в секторах автомобильного AI и промышленной автоматизации.

Распространение приложений, основанных на AI, в сфере периферийных вычислений, автономных транспортных средств и высокочастотной торговли дополнительно ускоряет принятие передовых интерфейсов HBM. По мере усложнения и увеличения объемов моделей AI, необходимость в более высокой пропускной способности памяти и меньшей задержке заставляет дизайнеров чипов принимать стандарты HBM2E, HBM3 и новые стандарты HBM4, как определено JEDEC Solid State Technology Association.

В заключение, рынок проектирования интерфейсов HBM для AI-ускорителей готов к значительному расширению к 2030 году, с сильным ростом в Азиатско-Тихоокеанском регионе и Северной Америке и четкой тенденцией к более высокой пропускной способности и более энергоэффективным решениям для памяти.

Драйверы и проблемы: требования к производительности, эффективность потребления энергии и сложности интеграции

Стремительная эволюция задач искусственного интеллекта (AI) создала небывалые требования к подсистемам памяти, что делает память высокой полосы пропускания (HBM) критическим компонентом для AI-ускорителей следующего поколения. Проектирование интерфейсов HBM должно учитывать несколько ключевых драйверов и вызовов, особенно в областях производительности, энергоэффективности и сложности интеграции.

Требования к производительности: AI-ускорители требуют огромной пропускной способности памяти, чтобы обеспечивать данные для вычислительных движков, особенно для моделей глубокого обучения с миллиардами параметров. HBM, с его 3D-структурой и широкой I/O, предлагает пропускные способности, превышающие 1 ТБ/с в последних генерациях. Тем не менее, для достижения этого на практике требуется тщательное проектирование интерфейса, чтобы минимизировать задержку, максимизировать пропускную способность и обеспечивать целостность сигнала на высоких скоростях передачи данных. Интерфейс также должен поддерживать эффективные схемы перемещения данных, типичные для рабочих нагрузок AI, такие как большие матричные умножения и операции с тензорами, которые создают дополнительную нагрузку на контроллеры памяти и соединения.

Энергоэффективность: По мере масштабирования AI-ускорителей потребление энергии становится критическим ограничением как для развертываний в центрах обработки данных, так и для периферийных приложений. Близость HBM к процессору и использование черезкремниевых vias (TSV) уменьшают потребление энергии на бит по сравнению с традиционной памятью DDR. Тем не менее, проектирование интерфейса должно дополнительно оптимизировать потребление энергии, используя передовые технологии передачи сигналов, динамическое управление напряжением и частотой и интеллектуальное управление питанием. Балансировка высокой пропускной способности с низким потреблением энергии является постоянной задачей, особенно по мере роста емкости и скорости стеков памяти. Такие организации, как Samsung Electronics Co., Ltd. и Micron Technology, Inc., активно разрабатывают новые поколения HBM с улучшенной энергоэффективностью.

Сложности интеграции: Интеграция HBM с AI-ускорителями требует значительных сложностей упаковки и уровня системы. Физическое наслоение чипов памяти и их подключение к процессору через кремниевые интерпозеры или передовые подложки требуют точного производства и термического управления. Целостность сигнала, электромагнитные помехи и механическое напряжение должны быть учтены для обеспечения надежной работы. Более того, интерфейс должен быть совместим с развивающимися стандартами, такими как те, которые определены JEDEC Solid State Technology Association, для обеспечения совместимости и будущей масштабируемости. Сложности возрастает, поскольку ускорители принимают архитектуры на основе чиплетов, требуя надежных решений интерфейса HBM, которые могут поддерживать гетерогенную интеграцию.

В заключение, проектирование интерфейсов HBM для AI-ускорителей в 2025 году формируется необходимостью предоставления экстремальной пропускной способности, поддержания энергоэффективности и управления сложностями продвинутой интеграции, при этом следя за быстрыми инновациями в аппаратном обеспечении AI.

Новые применения: AI, HPC, центры данных и периферийные вычисления

Стремительное развитие искусственного интеллекта (AI), высокопроизводительных вычислений (HPC), центров обработки данных и периферийных вычислений вызывает неслыханный спрос на пропускную способность и эффективность памяти. Проектирование интерфейса памяти высокой полосы пропускания (HBM) стало краеугольной технологией для AI-ускорителей, обеспечивая массированную параллельность и пропускную способность данных, необходимые для современных нагрузок глубокого обучения и аналитики. HBM достигает этого, накладывая несколько чипов ДРАМ вертикально и соединяя их через кремниевые vias (TSV), что приводит к значительно большей пропускной способности и более низкому потреблению энергии по сравнению с традиционными интерфейсами памяти.

В AI-ускорителях, таких как те, что разработаны NVIDIA Corporation и Advanced Micro Devices, Inc. (AMD), интерфейсы HBM критически важны для передачи данных тысячам вычислительных ядер без узких мест. Последние стандарты HBM3 и HBM3E, как определено JEDEC Solid State Technology Association, поддерживают пропускные способности, превышающие 1 ТБ/с на стек, что жизненно необходимо для обучения крупных нейронных сетей и реального вывода в центрах обработки данных. Эти интерфейсы плотно интегрированы с кристаллом ускорителя с использованием передовых технологий упаковки, таких как 2.5D и 3D интеграция, что минимизирует потери сигнала и задержки.

В средах HPC высокая пропускная способность и энергоэффективность HBM используются для ускорения научных симуляций, финансового моделирования и других задач, требующих интенсивных данных. Суперкомпьютеры, такие как те, что построены Cray Inc. и Fujitsu Limited, используют процессоры с поддержкой HBM для достижения целей по производительности на уровне петаскал и эксаскал. Проектирование интерфейса должно учитывать такие вызовы, как целостность сигнала, термическое управление и коррекция ошибок, чтобы обеспечить надежную работу под экстремальными нагрузками.

Устройства периферийных вычислений, которые требуют компактных форм-факторов и низкого потребления энергии, также начинают внедрять интерфейсы HBM. Компании, такие как Samsung Electronics Co., Ltd. и SK hynix Inc., разрабатывают решения HBM, адаптированные для чипов AI на периферии, балансируя потребности в пропускной способности с жесткими требованиями к энергии и теплоте.

Смотрим в будущее на 2025 год, дальнейшее усовершенствование проектирования интерфейсов HBM будет решающим для поддержки следующего поколения AI, HPC и периферийных приложений. Инновации в упаковке, передаче сигналов и архитектурах контроллеров памяти еще больше повысят масштабируемость и эффективность AI-ускорителей, обеспечивая, чтобы пропускная способность памяти соответствовала экспоненциальному росту вычислительного спроса.

Анализ цепочки поставок и экосистемы

Цепочка поставок и экосистема проектирования интерфейсов памяти высокой полосы пропускания (HBM) в AI-ускорителях характеризуется сложной сетью производителей полупроводников, поставщиков памяти, фабрик и поставщиков средств проектирования. HBM с его вертикально уложенными чипами ДРАМ и широкой интерфейсом является критически важным элементом для AI-ускорителей, предлагая пропускную способность и энергоэффективность, необходимые для крупных задач машинного обучения. Проектирование и интеграция интерфейсов HBM требуют тесного сотрудничества между поставщиками памяти, такими как Samsung Electronics Co., Ltd., Micron Technology, Inc. и SK hynix Inc., и ведущими дизайнерами чипов AI, такими как NVIDIA Corporation и Advanced Micro Devices, Inc. (AMD).

Экосистема дополнительно поддерживается передовыми технологиями упаковки и соединения, такими как кремниевые интерпозеры и интеграция 2.5D/3D, предоставляемыми фабриками, такими как Taiwan Semiconductor Manufacturing Company Limited (TSMC) и Intel Corporation. Эти фабрики обеспечивают физическую интеграцию стеков HBM с логическими кристаллами, обеспечивая целостность сигнала и термическое управление при высоких скоростях передачи данных. Поставщики средств проектирования (EDA), включая Synopsys, Inc. и Cadence Design Systems, Inc., предлагают специализированные решения IP и верификации для удовлетворения строгих требований к времени, энергии и надежности интерфейсов HBM.

Усилия по стандартизации, возглавляемые организациями, такими как JEDEC Solid State Technology Association, играют важную роль в определении спецификаций интерфейсов HBM и обеспечении совместимости по всей цепочке поставок. Быстрая эволюция стандартов HBM (например, HBM3, HBM3E) требует от участников экосистемы постоянно обновлять свои проектные потоки и производственные процессы. Кроме того, растущий спрос на AI-ускорители в центрах обработки данных и периферийных устройствах ускоряет инвестиции в расширение мощностей и устойчивость цепочки поставок, что стало очевидным в недавних заявлениях крупнейших партнеров по памяти и фабрикам.

В заключение, экосистема проектирования интерфейсов HBM для AI-ускорителей в 2025 году отмечена глубокими взаимозависимостями между поставщиками памяти, дизайнерами чипов, фабриками, поставщиками EDA и стандартными организациями. Эта совместная среда необходима для предоставления высокопроизводительных, энергоэффективных подсистем памяти, которые обеспечивают новые рабочие нагрузки AI.

Будущий прогноз: разрушительные технологии и интерфейсы HBM нового поколения

Будущее проектирования интерфейсов высокой полосы пропускания (HBM) для AI-ускорителей должно претерпеть значительные трансформации, вызванные разрушительными технологиями и эволюцией стандартов HBM следующего поколения. Поскольку рабочие нагрузки AI продолжают требовать более высокой пропускной способности памяти и меньшей задержки, индустрия движется к более продвинутым решениям, таким как HBM3E и ранние исследования HBM4. Эти новые стандарты обещают обеспечить беспрецедентные скорости передачи данных, при этом HBM3E нацеливается на скорость до 9.2 Гбит/с на вывод и общие пропускные способности, превышающие 1.2 ТБ/с на стек, что является критическим шагом для обучения AI и вывода в больших масштабах (Samsung Electronics).

Разрушительные интерфейсные технологии также выходят на передний план, чтобы решить проблемы целостности сигнала, подачи энергии и термического управления, связанные с наслоением большего количества чипов памяти и увеличением плотности I/O. Инновации, такие как передовые архитектуры черезкремниевых vias (TSV), улучшенные материалы интерпозера и приемы проектирования на базе чиплетов, позволяют более тесную интеграцию между AI-ускорителями и стековыми HBM. Например, использование кремниевых мостов и органических интерпозеров изучается для снижения затрат и повышения масштабируемости, при этом поддерживая высокоскоростную передачу, необходимую для HBM нового поколения (Advanced Micro Devices, Inc.).

Смотрим в будущее, интеграция HBM с новыми архитектурами AI-ускорителей, такими как те, которые используют упаковку 2.5D и 3D, еще больше размоет границы между памятью и вычислениями. Этот подход совместной упаковки ожидается, чтобы минимизировать движение данных, снизить энергопотребление и открыть новые уровни параллелизма для крупных языковых моделей и генеративных рабочих нагрузок AI. Лидеры отрасли также сотрудничают по новым протоколам интерфейса и схемам коррекции ошибок для обеспечения надежности и масштабируемости по мере роста пропускной способности памяти (Micron Technology, Inc.).

В заключение, будущее проектирования интерфейсов HBM для AI-ускорителей будет формироваться быстрыми прогрессами в технологиях памяти, инновациями в упаковке и совместным проектированием на уровне системы. Эти разработки должны переопределить рамки производительности аппаратного обеспечения AI в 2025 году и далее, позволяя следующую волну прорывов в машинном обучении и аналитике данных.

Стратегические рекомендации для заинтересованных сторон

Поскольку AI-ускорители все больше зависят от памяти высокой полосы пропускания (HBM) для удовлетворения требования к крупносмасштабным задачам машинного обучения и глубокого обучения, заинтересованные стороны — включая разработчиков чипов, системных интеграторов и операторов центров обработки данных — должны принимать долгосрочные стратегии для оптимизации проектирования интерфейса HBM. Следующие рекомендации направлены на решение развивающегося ландшафта интеграции HBM в AI-аппаратное обеспечение на 2025 год и далее.

- Приоритет совместного проектирования памяти и вычислений: Совместная разработка между командами памяти и вычислений необходима. Совместно оптимизируя интерфейс HBM с архитектурой AI-ускорителя, заинтересованные стороны могут минимизировать задержки и максимизировать пропускную способность. Компании, такие как Samsung Electronics Co., Ltd. и Micron Technology, Inc., демонстрировали преимущества таких интегрированных подходов в своих последних решениях HBM.

- Принять последние стандарты HBM: Оставаться в курсе последних стандартов HBM, таких как HBM3 и новые HBM4, обеспечивает совместимость и доступ к более высоким пропускным способностям и улучшенной энергоэффективности. JEDEC Solid State Technology Association регулярно обновляет эти стандарты, и раннее внедрение может обеспечить конкурентное преимущество.

- Инвестировать в передовые технологии упаковки: Упаковка 2.5D и 3D, такие как кремниевые интерпозеры и черезкремниевые vias (TSV), являются критически важными для эффективного проектирования интерфейсов HBM. Сотрудничество с такими специалистами по упаковке, как Taiwan Semiconductor Manufacturing Company Limited (TSMC), может помочь заинтересованным сторонам использовать передовые решения по соединениям.

- Оптимизировать подачу энергии и термическое управление: По мере увеличения плотности и скорости стеков HBM подача энергии и рассеивание тепла становятся все более сложными. Заинтересованные стороны должны инвестировать в передовые интегральные схемы управления питанием и инновационные решения для охлаждения, сотрудничая с партнерами, такими как CoolIT Systems Inc. для термического управления.

- Содействовать сотрудничеству в экосистеме: Участие в отрасле, консорциумах и органах стандартизации, таких как OIF (Оптический интерсетевой форум), может помочь заинтересованным сторонам быть в курсе нововведений в интерфейсах и требований к совместимости.

Внедрив эти стратегические рекомендации, заинтересованные стороны могут гарантировать, что их разработки интерфейсов HBM для AI-ускорителей останутся надежными, масштабируемыми и устойчивы к будущему, поддерживая следующее поколение рабочих нагрузок AI.

Источники и ссылки

- Micron Technology, Inc.

- NVIDIA Corporation

- JEDEC Solid State Technology Association

- Amkor Technology, Inc.

- Cray Inc.

- Fujitsu Limited

- Synopsys, Inc.

- OIF (Оптический интерсетевой форум)