背板连接器在高速PCB设计中的关键作用:释放下一代性能和可靠性。发现塑造您电路的最新创新和行业变革。

- 最新消息:背板连接器技术的最新进展

- 背板连接器在高速PCB设计中为何重要

- 关键性能指标:信号完整性、带宽和串扰

- 高速背板集成的设计挑战与解决方案

- 新兴标准和合规要求

- 行业案例研究:成功故事和经验教训

- 未来趋势:人工智能、5G和背板创新的下一波浪潮

- 来源和参考文献

最新消息:背板连接器技术的最新进展

背板连接器技术的最新进展正在显著影响高速PCB设计,使得更高的数据速率、改善的信号完整性和更大的系统可靠性成为可能。其中一个最显著的突破是开发了支持每差分对超过56 Gbps数据速率的连接器,满足了数据中心、5G基础设施和高性能计算等应用日益增长的需求。制造商正在利用新材料和优化的接触几何形状来最小化插入损耗和串扰,这对于在多千兆比特速度下维护信号质量至关重要。例如,TE Connectivity的低轮廓屏蔽连接器的推出,通过优化针脚布局,减少了电磁干扰(EMI),并改善了阻抗控制。

另一个显著的趋势是集成先进的制造技术,如精密冲压和激光焊接,这增强了连接器的一致性和机械强度。此外,Molex注意到,采用表面贴装技术(SMT)的背板连接器正在简化组装流程,并提高连接器密度。这些创新还通过使用基于仿真的设计工具来实现,使工程师能够在制造之前优化连接器性能。

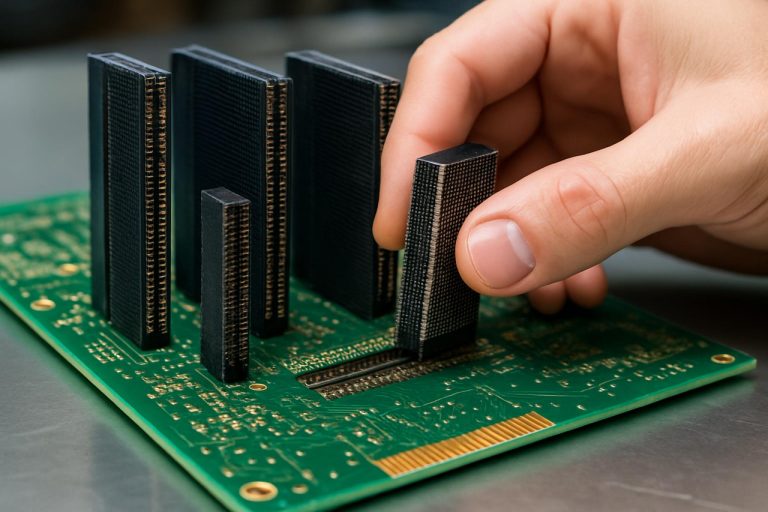

此外,业界正在见证模块化和可扩展连接器系统的出现,这使复杂系统中的升级和维护变得更加容易。这些进展共同确保背板连接器在下一代高速PCB设计中仍然是一个关键的推动者,支持对更大带宽和系统灵活性的不断追求。

背板连接器在高速PCB设计中为何重要

背板连接器在高速PCB设计中起着关键作用,作为复杂电子系统中多个印刷电路板之间的关键接口。随着数据中心、电信和高性能计算等应用的数据速率不断攀升,背板连接器的性能直接影响到整个系统的完整性和可靠性。高速信号在互连点特别容易受到损耗、反射和串扰的影响,从而使背板连接器的选择和设计成为信号质量和系统带宽的关键决定因素。

现代背板连接器旨在最小化插入损耗、回波损耗和电磁干扰,这些都是在多千兆比特速度下维持信号保真度所必需的。它们的机械强度确保了可靠的配合循环和对准,这对于需要频繁更换或升级模块的系统至关重要。此外,先进的连接器设计包含了差分对布线、屏蔽和优化接触几何形状等特征,以支持诸如PCIe、以太网和InfiniBand等高速串行协议 Samtec。

背板连接器的重要性不仅体现在电气性能上;它们还影响系统的可扩展性、热管理和维护便利性。选择合适的连接器可以实现更高的端口密度和未来兼容性,为下一代数据速率铺平道路,而不恰当的选择可能成为限制系统性能和升级能力的瓶颈 Molex。总之,背板连接器不仅仅是被动组件,它们是塑造高速电子系统能力和寿命的战略性元素。

关键性能指标:信号完整性、带宽和串扰

在高速PCB设计中,背板连接器是关键组件,其性能采用几个关键指标进行评估:信号完整性、带宽和串扰。信号完整性指的是电气信号在穿过连接器时质量和形状的保留,这对于最小化数据错误和确保可靠通信是至关重要的。连接器内阻抗不连续、插入损耗和回波损耗等因素可能会降低信号完整性,尤其是在多千兆比特数据速率下。先进的背板连接器通过受控阻抗和优化接触几何形状进行设计以减轻这些影响,正如TE Connectivity所强调的那样。

带宽是另一个关键指标,表示连接器能够在不显著衰减或失真的情况下传输信号的最大频率范围。随着数据速率的提高,连接器必须支持更宽的带宽以适应PCIe Gen5和400G以太网等高速串行协议。连接器接触的物理设计、材料选择和镀层都影响其带宽能力,如 Samtec 所详细介绍的。

串扰是指相邻通道之间信号的不必要耦合,随着信号密度和速度的提高而变得越来越成问题。过多的串扰可能导致数据损坏并限制可实现的通道密度。现代背板连接器采用屏蔽、差分对布线和错位针脚排列来最小化串扰,如 Molex 所描述的。这些性能指标的仔细关注对于确保在先进电子系统中进行强大、高速数据传输至关重要。

高速背板集成的设计挑战与解决方案

将背板连接器集成到高速PCB设计中带来了独特的挑战,主要是由于现代应用对信号完整性的严格要求和越来越高的数据速率。其中一个主要问题是管理由连接器与PCB接口处阻抗不连续引起的信号损失和反射。当数据速率超过10 Gbps时,甚至微小的不匹配也可能导致信号质量显著下降,从而导致比特错误率增加和系统可靠性降低。密集连接器阵列之间的相邻高速通道的串扰更进一步复杂了设计,需要仔细的布局和屏蔽策略。

为了应对这些挑战,设计师采用了若干解决方案。先进的背板连接器采用受控阻抗和优化接触几何形状来最小化插入损耗和回波损耗。使用差分信号与连接对之间的接地屏蔽结合,有助于抑制串扰和电磁干扰。精心设计的PCB堆叠,包括低损耗介质材料和精确的走线设计,对于在背板接口上保持信号完整性至关重要。广泛使用仿真工具来建模高频效应,验证连接器性能,从而减少昂贵的设计迭代风险。此外,遵循 IEEE 及国际电工委员会(IEC)等行业标准,确保多厂商环境中的互操作性和可靠性。

最终,成功的高速背板集成依赖于将先进的连接器技术、细致的PCB设计和严格的验证结合起来的整体方法,以便在数据集中的高需求应用中实现稳健性能。

新兴标准和合规要求

随着高速PCB设计中数据速率的不断提高,背板连接器必须遵守新兴标准和合规要求,以确保信号完整性、互操作性和系统可靠性。现代标准如PCI Express (PCIe) Gen 5/6、Ethernet (25/50/100/400G)和开放计算项目(OCP)规格正在推动背板连接器技术的发展。这些标准定义了严格的电气、机械和环境参数,包括连接器必须满足的插入损耗、串扰、阻抗控制和电磁兼容性(EMC),以支持多千兆信号速率。

遵循这些标准不是可选的;它对确保背板连接器能够可靠地传输高速信号而不发生过度降解或数据错误至关重要。例如,PCI-SIG的PCIe 6.0规格要求极低的插入损耗和严格的阻抗公差,而 IEEE 802.3以太网标准规定了背板通道的回波损耗和串扰限制。此外,开放计算项目等行业联盟正在引入用于模块化和高密度背板连接器的开放标准,以促进跨供应商的互操作性。

制造商必须通过严格的合规测试验证其连接器设计,包括眼图分析、比特错误率(BER)测试和电磁干扰(EMI)评估。遵循这些新兴标准不仅确保了合规性,还使设计在不断发展的数据中心和网络需求面前具备了未来适应能力,支持在高速应用中的可扩展性和长期可靠性。

行业案例研究:成功故事和经验教训

行业案例研究提供了关于将背板连接器集成到高速PCB设计中的实际挑战和解决方案的宝贵见解。例如,一家领先的电信公司在升级其网络交换机以支持56 Gbps数据速率时面临重大的信号完整性问题。通过与Molex合作,该公司采用了具有优化接触几何形状和低串扰设计的先进背板连接器,结果使眼图性能提升了30%,并能够在更高速度下可靠运行。

另一个显著的例子来自数据中心行业,一家主要的服务器制造商希望在不扩展其背板物理占地面积的情况下增加带宽。通过利用TE Connectivity的高密度、低插入损耗连接器,设计团队成功地在保持信号完整性的同时将每个背板的通道数量翻倍。该项目强调了连接器与PCB布局团队之间早期共同设计的重要性,以及使用先进仿真工具来预测和缓解潜在问题的必要性。

然而,并非所有实现都是顺利的。一个涉及医疗成像设备提供商的案例显示,未能充分关注连接器阻抗匹配导致意外的EMI问题,迫使重新设计,增加了成本。这强调了在高速应用中,彻底的布局前分析和与连接器制造商(如Amphenol)密切合作的重要性。

这些案例研究共同证明,正确选择和集成背板连接器结合强大的工程流程,对于在要求苛刻的高速PCB环境中实现高性能和可靠性至关重要。

未来趋势:人工智能、5G和背板创新的下一波浪潮

人工智能(AI)和5G等技术的快速发展正在从根本上重塑高速PCB设计中对背板连接器的要求。随着AI工作负载对数据吞吐量和超低延迟的需求不断增加,以及5G基础设施对带宽和可靠性的更高要求,背板连接器必须发展以支持远超56 Gbps的数据速率,某些下一代设计的目标是112 Gbps及更高。这需要在信号完整性、串扰抑制和电磁干扰(EMI)屏蔽方面的创新,以及采用先进的材料和制造技术。

AI驱动的设计工具也开始在优化连接器几何形状和布置方面发挥重要作用,使得信号行为的预测建模和潜在瓶颈或故障点的自动检测成为可能。这些工具可以加速开发周期,改善高速互连的性能,如TE Connectivity所强调的。同样,5G和边缘计算的普及正在推动对模块化、可扩展的背板架构的需求,这些架构可以轻松升级或重新配置以适应不断变化的标准和增加的数据负载,如Molex所讨论的。

展望未来,人工智能、5G与光互连等新兴技术的融合预计将进一步改变背板连接器的设计。混合电气光连接器、先进的热管理解决方案以及与系统级架构的更紧密集成,将是满足下一代高速PCB性能和可靠性需求的关键。